# EVALUATING HARDWARE/SOFTWARE PARTITIONING AND AN EMBEDDED LINUX PORT OF THE VIRTEX-II PRO DEVELOPMENT SYSTEM

# By

# HSIANG-LING JAMIE LIN

A thesis submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN COMPUTER ENGINEERING

WASHINGTON STATE UNIVERSITY School of Electrical Engineering and Computer Science

MAY 2006

| To the Faculty of Washington State U                                 | niversity:                                                                 |

|----------------------------------------------------------------------|----------------------------------------------------------------------------|

| The members of the Commit HSIANG-LING JAMIE LIN find it sa accepted. | tee appointed to examine the thesis of tisfactory and recommend that it be |

|                                                                      | Chair                                                                      |

|                                                                      |                                                                            |

|                                                                      |                                                                            |

# **ACKNOWLEDGMENT**

I would like to express my gratitude to those who have helped me academically and personally in the completion of the thesis. Many thanks to my advisor, Dr. Jabulani Nyathi, for his assistance on my research and efforts in searching for support. I have learned a great deal of knowledge from him. He has been very patient and kind with a paranoid student like myself. I acknowledge Clint Cole and Digilent Inc., for all the help during the years I have been in Pullman and the sponsorship on my research.

Thank you Hui-ling Lin and Chuan Shiu, for all personal favors over the years and for offering me a great place to stay when I need a break from school. I would like to acknowledge Lee Verberne, for his inspiration in the technical field. Thank you Min Lin, for being a good friend. I wouldn't have gone abroad for college at the first place without meeting an adventure pal like you. Thank you Judi and Gary Wutzke, for the love and support as a family. Thank you my friends, especially Charles Chen, Wendy Chao, Priscilla Septiany, and Yuki Makino, for the great friendship and encouragement.

Last, I would like to acknowledge myself. Without my persistence in all difficulties I have faced, I wouldn't have gone this far.

EVALUATING HARDWARE/SOFTWARE PARTITIONING

AND AN EMBEDDED LINUX PORT OF THE VIRTEX-II

PRO DEVELOPMENT SYSTEM

**Abstract**

by Hsiang-ling Jamie Lin, M.S. Washington State University

May 2006

Chair: Jabulani Nyathi

The embedded system application space is growing at a fast pace and has a very

wide range that encompasses minute sensor nodes through large FPGA based systems

with multiple embedded processors within a single chip. Regardless of the application

type and size; testing, monitoring and debugging of these systems remain central to their

success as solutions to today's problems. The Virtex-II Pro development system offered

by Xilinx is an embedded development environment that has benefited greatly from the

system on chip design approach. It is a programmable system with two embedded IBM

Power PCs and an FPGA all of which are connected via IBM's core-connect bus. This

makes the system suitable for emulating applications in actual hardware while offering at

speed testing. This thesis examines several embedded systems design considerations such

as the hardware/software partitioning and the timeliness of event handling. The objective

is to provide a stable development environment that exploits the hardware features of the

board to allow for ease of use particularly in the educational sector. Digital adaptive

filtering is considered to demonstrate the benefits and flexibility offered by this

development system. Significant performance gains are recorded with a well-partitioned

iv

finite impulse response filter showing that the software-based filter is outperformed by 72%.

Another aspect of this research is to port an embedded operating system to manage the hardware and offer design flexibility. The embedded Linux kernel has been considered as the suitable real-time operating system (RTOS) and the first challenge is to ensure that the embedded cores are simultaneously visible to the operating system and user under shared memory system environment. This approach has been chosen with the view that tasks executing on any of the processors will for the most part be required to work towards a common goal. The shared memory approach has not been a success due to the cache coherence issues, however, sample device drivers under the Linux kernel have been written and the kernel successfully ported to run on a single processor.

# TABLE OF CONTENTS

|                                                 | Page |

|-------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                | iii  |

| ABSTRACT                                        | iv   |

| LIST OF TABLES                                  | ix   |

| LISTOF FIGURES                                  | X    |

| CHAPTER                                         |      |

| 1. INTRODUCTION                                 | 1    |

| 1.1 The Xilinx Virtex-II Pro Platform FPGAs     | 1    |

| 1.2 The Xilinx EDK                              | 3    |

| 1.3 Research Brief                              | 6    |

| 1.4 Conclusion                                  | 7    |

| 2. BACKGROUND INFORMATION                       | 8    |

| 2.1 The Virtex-II Pro Development System        | 8    |

| 2.2 Embedded Applications Design                | 10   |

| 2.2.1 Design Specification and Components       | 10   |

| 2.2.2 Implementation                            | 12   |

| 2.3 Conclusion                                  | 17   |

| 3. DISTRIBUTED SYSTEM V.S. SHARED MEMORY SYSTEM | 19   |

| 3.1 Parallel Computing                          | 19   |

| 3.2 Using Dual PowerPC Cores                    | 22   |

|    | 3.2.1 A Simple Shared-Memory System                         | 22 |

|----|-------------------------------------------------------------|----|

|    | 3.3 The Virtex-II Pro Distributed System                    | 28 |

|    | 3.4 Conclusion                                              | 28 |

| 4. | EMBEDDED LINUX ON THE VIRTEX-II PRO SYSTEM                  | 29 |

|    | 4.1 Background                                              | 29 |

|    | 4.2 Embedded Linux on the Virtex-II Pro Development System  | 29 |

|    | 4.3 Requirements for the Linux Port                         | 31 |

|    | 4.4 Porting Linux                                           | 34 |

|    | 4.5 Comments on Symmetric Multiprocessing                   | 42 |

|    | 4.6 Linux Device Drivers                                    | 42 |

|    | 4.6.1 Loadable Kernel Module                                | 43 |

|    | 4.6.2 Loadable Kernel Module with User Programs             | 44 |

|    | 4.7 Conclusion                                              | 46 |

| 5. | HARDWARE SOFTWARE PARTITIONING                              | 47 |

|    | 5.1 Background                                              | 47 |

|    | 5.1.1 Digital Signal Processing                             | 48 |

|    | 5.2 FIR Filter Design                                       | 48 |

|    | 5.2.1 FIR Filter Specifications                             | 52 |

|    | 5.2.2 FIR Filter Plots                                      | 53 |

|    | 5.2.3 Software Based Audio Filtering Design                 | 56 |

|    | 5.2.4 Hardware Software Partitioning Audio Filtering Design | 56 |

|    | 5.3 System Performance                                      | 57 |

|    | 5.4 Adaptive Filtering                                      | 59 |

| 5.5 Conclusion                            | 60 |

|-------------------------------------------|----|

| 6. RESEARCH CONTRIBUTIONS AND FUTURE WORK | 62 |

| BIBLIOGRAPHY                              | 63 |

| APPENDIX                                  |    |

| A. NETWORKING APPLICATION                 | 66 |

| B. DUAL-CORE DESIGN                       | 75 |

| C. LOADABLE MODULE                        | 77 |

| D. ENHANCED LOADABLE MODULE               | 80 |

| E. SOFT AUDIO FILTERING APPLICATION       | 84 |

| F HARD/SOFT AUDIO FILTERING APPLICATION   | 87 |

# LIST OF TABLES

|    |                                                                      | Page |

|----|----------------------------------------------------------------------|------|

| 1. | Table 5.1: FIR Filter specifications                                 | 53   |

| 2. | Table 5.2: Execution time measurements for the band-pass filter      | 58   |

| 3. | Table 5.3: Execution time measurements for the low-pass filter       | 58   |

| 4. | Table 5.4: Execution time measurements for the high-pass filter      | 58   |

| 5. | Table 5.5: Execution time measurements for the AC97 codec read/write | 59   |

| 6. | Table 5.6: Voice filter specification.                               | 60   |

# LIST OF FIGURES

|     |                                                                       | Page |

|-----|-----------------------------------------------------------------------|------|

| 1.  | Figure 1.1: System evolution [1]                                      | 1    |

| 2.  | Figure 1.2: The Virtex-II Pro development system                      | 3    |

| 3.  | Figure 1.3: The Xilinx EDK tool chain [1]                             | 4    |

| 4.  | Figure 2.1: System block diagram                                      | 14   |

| 5.  | Figure 2.2: Peripherals in the system                                 | 14   |

| 6.  | Figure 2.3: Bus connections                                           | 15   |

| 7.  | Figure 2.4: Sample outputs                                            | 16   |

| 8.  | Figure 3.1: Shared memory system                                      | 20   |

| 9.  | Figure 3.2: Distributed memory system                                 | 21   |

| 10. | Figure 3.3: Hybrid distributed-shared memory system                   | 21   |

| 11. | Figure 3.4: Shared memory system block diagram                        | 23   |

| 12. | Figure 3.5: Bus connections for the shared memory system              | 24   |

| 13. | Figure 3.6: BRAM ports connected to the controller ports              | 24   |

| 14. | Figure 3.7: Address Map.                                              | 25   |

| 15. | Figure 3.8: Ports for PPC1                                            | 26   |

| 16. | Figure 3.9: Added ports for PLB and BRAM controller connected to PPC1 | 26   |

| 17. | Figure 3.10: Sample Outputs                                           | 27   |

| 18. | Figure 4.1: Loadable module output                                    | 44   |

| 19. | Figure 4.2: Enhanced loadable module output                           | 45   |

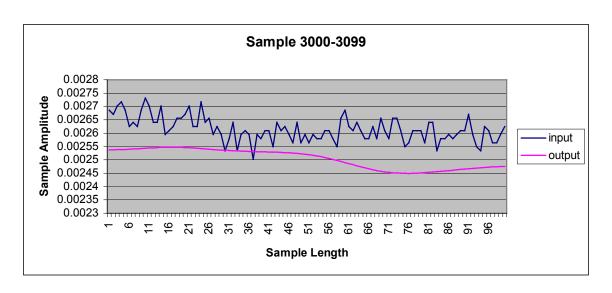

| 20. | Figure 5.1: Sample plot #1 of the low-pass filter                     | 54   |

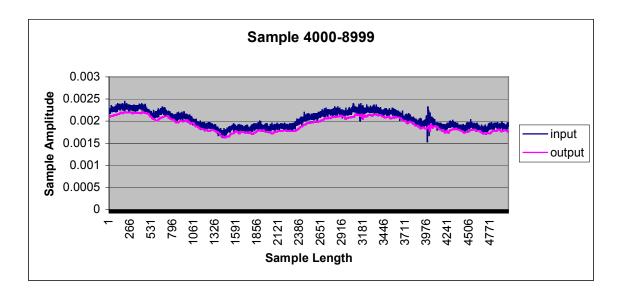

| 21. | Figure 5.2: Sample plot #2 of the low-pass filter                     | 54   |

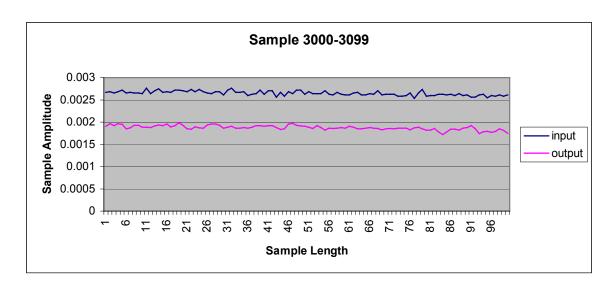

| 22. | Figure 5.3: Sample plot #1 of the high-pass filter                    | 55   |

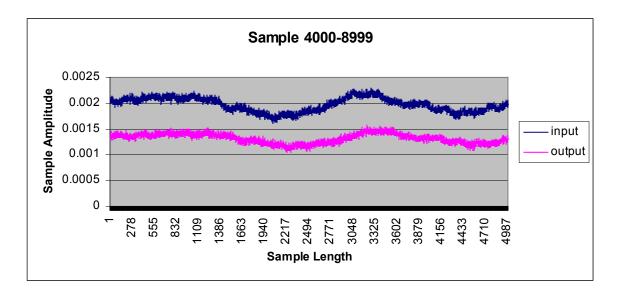

| 23. Figure 5.4: Sample plot #2 of the high-pass filter                               | 55 |

|--------------------------------------------------------------------------------------|----|

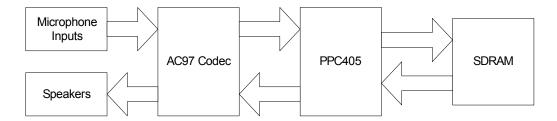

| 24. Figure 5.5: System flow diagram for the software based audio filtering design    | 56 |

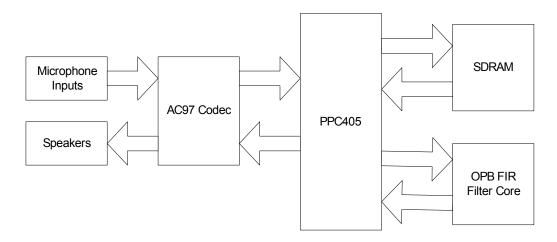

| 25. Figure 5.6: System flow diagram for the hardware/software audio filtering design | 57 |

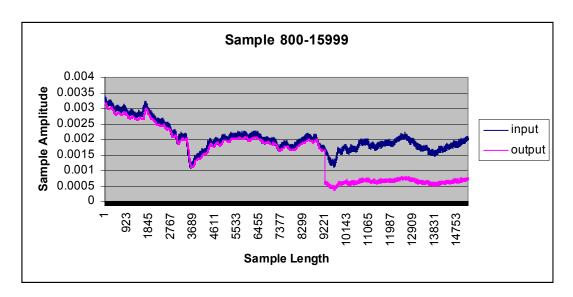

| 26. Figure 5.7: Input/output plot for the adaptive filter                            | 60 |

# **Dedication**

This thesis is dedicated to my father, who has passed.

He would be so proud of my achievement in education like he had been.

This thesis is dedicated to my family, especially my mother.

They have supported my stubborn and determined mind with love,

no matter how unreasonable I am sometimes.

# **CHAPTER ONE**

# **INTRODUCTION**

# 1.1 The Xilinx Virtex-II Pro Platform FPGAs

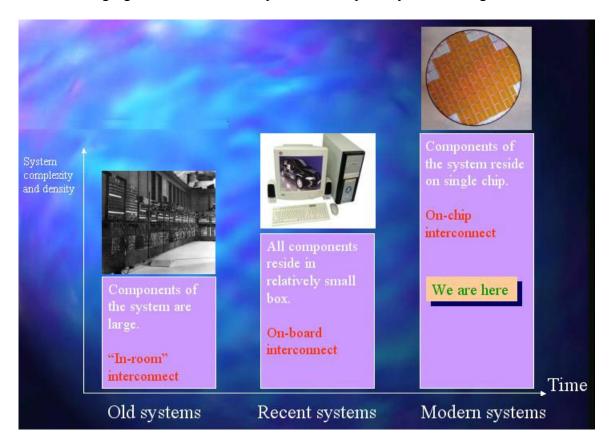

Before we study embedded systems, it is useful to look at the system evolution.

The following figure shows the development of computer systems through the time.

Figure 1.1: System evolution [1]

From a system that occupied an entire room to a handheld computer that has the size of a pencil box, System-on-a-Chip (SoC) has become an important role in the system development. The embedded computing filed is growing fast, and new technologies

continue to be developed. The Xilinx Virtex-II Pro FPGA is such an example. It has taken system-on-a-chip to the next level: system on a programmable chip.

Field Programmable Gate Array (FPGA) and microprocessors accomplish different tasks. FPGAs are configurable and re-programmable digital logic devices, and programming code is usually written in Hardware Description Languages (HDL). Microprocessors execute predefined commands, and do not have much flexibility. Engineers usually write programs for microprocessors in a language such as C. As applications become more complex, use of one or the other becomes insufficient. Traditionally, engineers program an FPGA and a microprocessor individually. If there is a need for the two to communicate, a link can be established by manually setting it up using expansion connectors or other techniques. The Virtex-II Pro development system (Figure 1.2) integrates two technologies. It has two hard PowerPC405 processors, one soft MicroBlaze processor, and an FPGA on a single chip. With such a powerful chip, design of embedded applications becomes more flexible and efficient. The communication latency between a processor and hardware Intellectual Property (IP) is reduced, because of direct connections between them and they even share memory. The FPGA and processors co-existence feature allows us to perform hardware software partitioning. We can also take the advantage of dual cores to design a parallel computing system. Other benefits of this integration include ease of testing, monitoring and debugging both hardware and software components of the system on a chip. The development system also comes with expansion connectors. Commonly used devices such as the USB port, serial port, audio, video, and so on are already built on this board. However, if a project requires some external device, it can be attached through these expansion connectors.

Figure 1.2: The Virtex-II Pro development system

# 1.2 The Xilinx EDK

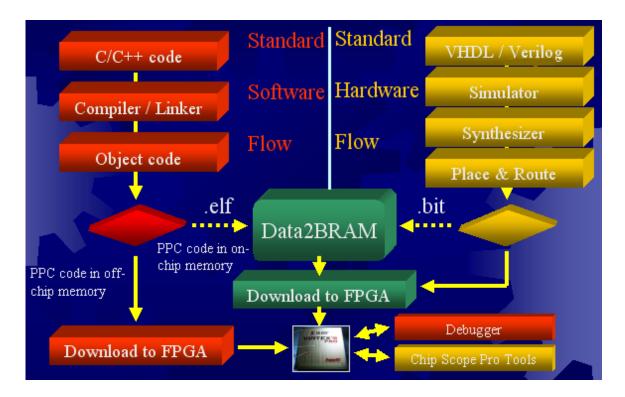

The Xilinx Embedded Development Kit (EDK) contains Embedded System Tools (EST), documentation, and Hardware IPs for the Xilinx embedded processors and peripherals [2]. Every embedded system design using the Xilinx EDK is divided into two parts: hardware design and software design. The Xilinx Platform Studio (XPS) provides an Integrated Development Environment (IDE) that combines hardware and software designs in one interface. The hardware specification and corresponding libraries can be generated based on user selections. We can access hardware components in a processor with appropriate drivers. We can also design custom IP cores for specific embedded system requirements. Once the hardware design is implemented and software programs are compiled, they can be combined into a bitstream and downloaded to the target system. Below is a detailed block diagram that shows the system design flow using the Xilinx EDK.

Figure 1.3: The Xilinx EDK tool chain [1]

At the end of hardware design, we will have a downloable bitstream. At the end of software design, we will have an executable binary for the software program. If the software program uses on-chip block RAMs, the object code (.elf) can be combined with the hardware bitstream (.bit) to form a new downloadable bitstream using the DATA2BRAM utility. DATA2BRAM takes the .bit file as an input, and adds new block RAM contents if there is any. This eliminates the need to re-implement the entire system after modifications have been made to the software. To debug a software program, we can use the software debugger that comes with the Xilinx EDK. Hardware debugging requires Xilinx ChipScope, if no other device such as an oscilloscope or a logic analyzer is available. The following lists the detailed steps for designing an embedded application using the Xilinx EDK [3]:

## Creating an Embedded Hardware System

This first step is to create a hardware platform, which contains processor information, buses, and peripheral devices attached to the processors. This is done in the Base System Builder (BSB) wizard. The Platform Generator (PlatGen) takes the hardware specification file, and generates netlists for the system.

# **Creating Software for the Embedded System**

XPS allows us to add software applications to available processors. The applications can be compiled with GCC like compilers.

### **Software Libraries**

Library Generator (LibGen) is used to generate software libraries. The output of LibGen is based on the hardware platform and user selected internal libraries.

## **System Implementation**

There are two ways to implement an embedded system design using the Xilinx EDK: Xflow and ISE Integration. Xflow implements a design directly in XPS. The main advantage of using Xflow is that we can have the entire design done in one GUI. However, Xflow does not give us direct controls of synthesis and implementation options. On the other hand, ISE and XPS integration allows us to control implementation and synthesis for the design, and add additional logic to the FPGA. The only drawback is that we have to work with two different software interfaces.

# Initialize the System and Download to the Board

The last step involves updating the hardware bitstream, and downloading the most recent bitstream to the board. The Virtex-II Pro development system configures

the board through JTAG. It automatically scans the JTAG chain and downloads the bitstream it finds.

### 1.3 Research Brief

The Virtex-II Pro development system is ideal for research and embedded system class projects. Students can experiment embedded applications on different devices on the board. By working with such a complex system, students can gain valuable experience in the embedded system field. A lot of the potential for this board remains unexplored. For example, running applications in embedded Linux on the board has been mentioned, but no work has been presented. Therefore, it is also an excellent choice for system-on-a-chip research projects.

The focus of the research has been to investigate potential educational experiments, ranging from an embedded operating system port to performance benefits offered by the integration of the embedded cores and the FPGA. Of particular interest is the investigation of the benefits and efficiency of system on a programmable chip, particularly the hardware software partitioning. With the Virtex-II Pro FPGA, we will be able to split tasks for computation efficiency. For example, the hardware multipliers can be used to improve performance of multiplication, which is slow if done in a processor. We can easily reduce the workload for processors by having hardware handle certain tasks, if such hardware has better performance over processors for these tasks. Since each processor has its own memory, we can have the processors perform independent tasks or work together towards a common goal. This research examines the above aspects of the Virtex-II Pro development system. The research also presents the pros and cons of having and not having an embedded operating system on this particular platform.

# 1.4 Conclusion

This chapter presents the research brief, and introduces the Xilinx Virtex-II Pro Platform FPGAs and EDK, which will be used for the research. System on a programmable chip takes the design of embedded applications to a new level. This research will explore the potentials and capabilities of the Virtex-II Pro Platform FPGAs.

In Chapter 2 we present information on the development system architecture, highlighting primarily features of interest. Chapter 3 presents parallel computing basics and how to build a dual-core system, while in Chapter 4 the Linux port along with host development system requirements are presented. The hardware and software partitioning approach is discussed in Chapter 5, and an elaborate digital signal processing example is also described and implemented in this chapter. Chapter 6 provides some concluding remarks and some directions on future work.

# **CHAPTER TWO**

# **BACKGROUND INFORMATION**

# 2.1 The Virtex-II Pro Development System

The Virtex-II Pro development system has just been introduced, and this chapter will present a deep look at its capability. The following is a list of important features of the development system [4]:

- Virtex-II Pro XC2VP30 FPGA with 30,816 Logic Cells, 136 18-bit multipliers,

2,448Kb of block RAM, one MicroBlaze Soft Processor, and two PowerPC405

Hard Processors

- DDR SDRAM DIMM that can accept up to 2-Gbyte of RAM

- 10/100 Ethernet port

- USB2 port

- Compact Flash card slot

- XSGA Video port

- Audio Codec

- SATA (Serial Advanced Technology Attachment), PS/2, and RS-232 ports

- High and Low Speed expansion connectors with a large collection of available expansion boards

- System ACE™ controller and Type II CompactFlash™ connector for FPGA configuration and data storage

Traditional embedded applications are controlled by micro-controllers. The micro-controller collects data, does computations, and then transfers data to some display if any. What tasks a micro-controller must perform depends on the application, but the micro-controller unit (MCU) has to do all the computational work. With the introduction of Virtex-II Pro Platform FPGAs, embedded application designs have moved to a new level of flexibility and efficiency. The IBM PowerPC405 core is a 32-bit RISC processor. It implements the 5-stage data path pipeline, and has 32 32-bit general-purpose registers and 16KB instruction and data caches. PowerPC405 processors have dedicated Harvard architecture controllers to interface instruction and data On-Chip-Memory (OCM). OCM is used as additional memory to the instruction and data caches, and provides memoryaccess performance same as a cache hit. The PowerPC405 is an implementation of the PowerPC embedded environment architecture. It provides high performance at low power consumption for embedded applications [5]. MicroBlaze is a soft processor. It is implemented using general logic primitives instead of a dedicating block in the FPGA. The MicroBlaze soft core allows a user to control the cache sizes and execution units [6]. It does not implement a Memory Management Unit (MMU), and so only operating systems lacking of MMU such as uClinux can be ported. This research focuses on the PowerPC processors. Further details of using the soft core are beyond the scope of the topic and will be omitted.

Evidently, with such a powerful FPGA, complex arithmetic and logic operations can be done in the hardware efficiently. The processors can handle software tasks as needed. The FPGA and processor co-design capability allows for easily solving complex engineering problems in a timely manner and within such a small system.

The bus architecture used on the Virtex-II Pro development system is the IBM CoreConnect standard. The architecture allows engineers to assemble custom SoC designs on the cores that support CoreConnect specifications. Processor Local Bus (PLB), On-chip Peripheral Bus (OPB), and Device Control Register (DCR) bus are included in the CoreConnect standard [7]. The PLB is fully synchronous and supports up to 16 master and 16 slave high bandwidth devices. The OPB is fully synchronous and supports up to 16 master and an unlimited number of slave lower bandwidth devices. The DCR bus provides processor blocks a mechanism to control peripheral devices on the FPGA. The bus architecture reduces the time and costs for SoC designs.

# 2.2 Embedded Applications Design

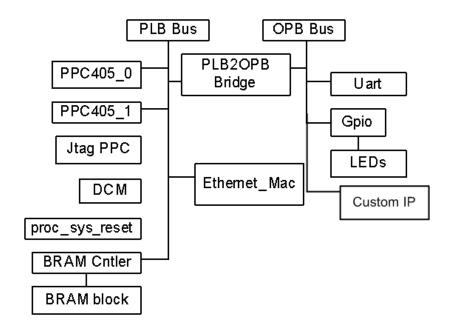

The Xilinx Platform Studio enables us to design both hardware and software specifications in one interface. There are many built-in peripherals we can choose from. We can also design custom peripherals. The development interface allows us to view system block diagrams, bus connections, address maps, and other design related components. To experiment with the Xilinx EDK in building embedded applications, a networking embedded application has been implemented. This design combines important features that a designer can use in Platform Studio.

# 2.2.1 Design Specification and Components

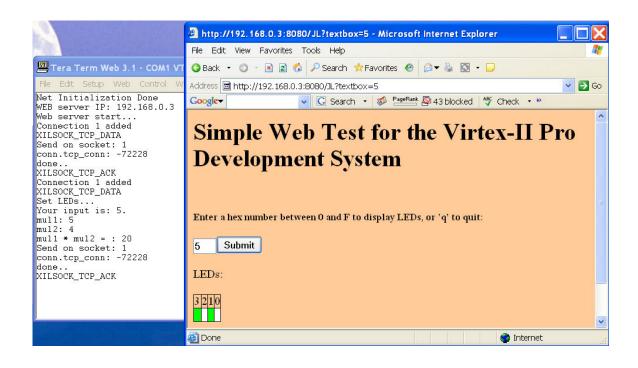

The design shows how to use UART, onboard general-purpose input/output (GPIO) registers, and Ethernet. A multiplier peripheral is added to show how a custom IP can be designed and imported to a project. The application does the following: When the server starts to run, the application accepts a user input from a web browser. The input value should be a hexadecimal number between 0 and F. The server processes this data,

and the value is displayed to the 4-bit LEDs and in the browser window. The multiplier takes the user input and multiplies it by 4 in the FPGA. The processor then reads the product from the FPGA and displays it to a terminal. The terminal shows the current input value, product, and web connection information. The exercise shows the benefits of system on a programmable chip enabling a user to interface the embedded core with the FPGA work that would otherwise require complex communication between the FPGA and the development host. The required components for this design are listed below:

### **PLB Ethernet**

Ethernet is considered as a high bandwidth IP, so it is attached to the processor as a PLB device. Xilnet is one of the Xilinx EDK built-in libraries. It provides functions for networking. For example, socket(), bind(), receive(), send(), etc. Xilinx has customized the standard networking functions to adapt their devices, so the usage might be slightly different. Before using any of the functions, one should consult the library specifications. To use Xilnet functions, we need to associate the Ethernet\_Mac device to the library, and run the Library Generator (LibGen) to generate corresponding libraries. To enable Xilnet, we simply select the option in the Software Platform Settings window.

### **OPB LEDs**

The LEDs are useful for displaying outputs. In this experiment, it is used to display the user input from a web browser.

### OPB RS232 UART

We will need a way to check if the application works correctly. The UART is used as the standard output for viewing the current information in the running application.

PLB BRAM Controller: 64KB

64KB of BRAM is used to store the application.

**OPB Multiplier**

This is a custom IP that multiplies two 32-bit numbers. The peripheral is used to

show how a custom IP can be designed and imported to the embedded

application. It takes a user input from a web browser, and multiplies the input by

4. The product is read by the processor to display in a terminal.

2.2.2 Implementation

Based on the components of the list above, a base system consisting of the

following components has been built:

PowerPC

Jtag PPC

4-Bit LEDs

Ethernet MAC controller: default setting

RS232 Uart: baudrate at 115200

PLB BRAM Controller: 64KB

A multiplier custom IP is built using the Create/Import Peripheral Wizard. The IP has

three registers: Reg0 and Reg1 for inputs, and Reg2 for the product. The read and write

processes are modified to meet the multiplier requirements. Also, a process is added for

the multiplication function. The following shows the code for these processes in the

user logic.vhd file:

MUL PROC: process(Bus2IP Clk) is

if Bus2IP Clk'event and Bus2IP Clk = '1' then

if Bus2IP Reset = '1' then

12

```

slv reg2 \le (others => '0');

else

slv reg2 <= slv reg0 * slv reg1;

end if;

end if;

end process MUL PROC;

SLAVE REG WRITE PROC: process(Bus2IP Clk) is

begin

if Bus2IP Clk'event and Bus2IP Clk = '1' then

if Bus2IP Reset = '1' then

slv reg0 \le (others => '0');

slv reg1 \leq (others \Rightarrow '0');

else

case slv_reg_write_select is

when "100" => slv reg0 <= Bus2IP Data(0 to C DWIDTH-1);

when "010" \Rightarrow slv reg1 \iff Bus2IP Data(0 to C DWIDTH-1);

when others => null;

end case;

end if;

end if;

end process SLAVE REG WRITE PROC;

SLAVE REG READ PROC: process(slv reg read select, slv reg0, slv reg1, slv reg2) is

begin

case slv reg read select is

when "100" => slv ip2bus data <= slv reg0;

when "010" => slv ip2bus data <= slv reg1;

when "001" => slv ip2bus data <= slv reg2;

when others \Rightarrow slv ip2bus data \iff (others \Rightarrow '0');

end case;

end process SLAVE REG READ PROC;

```

When a read is issued in the processor for reg2, the product of reg0 and reg1 will be sent from the FPGA. The following shows the system block diagram:

Figure 2.1: System block diagram

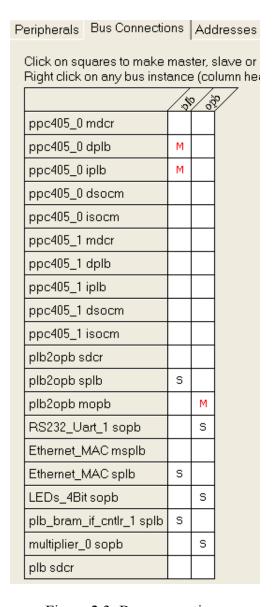

After adding the custom IP, the following peripherals and bus connections exist:

| Peripherals   Bus Connection                                                                                 | ons Addres                                                                                                                                            | ses Ports Parameters |  |

|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| Cells with white backgrounds can be edited. To delete peripherals, choose one or more rows and click Delete. |                                                                                                                                                       |                      |  |

| Peripheral                                                                                                   | HW Ver                                                                                                                                                | Instance             |  |

| ppc405                                                                                                       | 2.00.c 🔻                                                                                                                                              | ppc405_0             |  |

| ppc405                                                                                                       | 2.00.c 🔻                                                                                                                                              | ppc405_1             |  |

| jtagppc_cntlr                                                                                                | jtagppc_cntlr 2.00.a ▼ jtagppc                                                                                                                        |                      |  |

| proc_sys_reset                                                                                               | 1.00.a                                                                                                                                                | reset_block          |  |

| plb2opb_bridge                                                                                               | 1.01.a 🔻                                                                                                                                              | plb2opb              |  |

| opb_uartlite                                                                                                 | 1.00.b                                                                                                                                                | RS232_Uart_1         |  |

| plb_ethernet                                                                                                 | 1.01.a 🔻                                                                                                                                              | Ethernet_MAC         |  |

| opb_gpio                                                                                                     | 3.01.b 🔻                                                                                                                                              | LEDs_4Bit            |  |

| plb_bram_if_cntlr                                                                                            | plb_bram_if_cnttr     1.00.b     ▼ plb_bram_if_cnttr_1       bram_block     1.00.a     plb_bram_if_cnttr_1_bram       dcm_module     1.00.a     dcm_0 |                      |  |

| bram_block                                                                                                   |                                                                                                                                                       |                      |  |

| dcm_module                                                                                                   |                                                                                                                                                       |                      |  |

| multiplier 1.00.a multiplier_0                                                                               |                                                                                                                                                       | multiplier_0         |  |

Figure 2.2: Peripherals in the system

Figure 2.3: Bus connections

The software application code can be found in Appendix A. The following is a screenshot of sample outputs:

Figure 2.4: Sample outputs

# Output Log:

```

Net Initialization Done

WEB server IP: 192.168.0.3

Web server start...

Connection 1 added

XILSOCK TCP DATA

Send on socket: 1

conn.tcp conn: -72228

done..

XILSOCK TCP ACK

Connection \overline{1} added

XILSOCK TCP DATA

Set LEDs...

Your input is: 5.

mul1: 5

mul2: 4

mul1 * mul2 = : 20

Send on socket: 1

conn.tcp_conn: -72228

done..

XILSOCK TCP ACK

Connection 1 added

XILSOCK TCP DATA

Set LEDs...

Your input is: 9.

mul1: 9

mul2: 4

mul1 * mul2 = : 36

Send on socket: 1

```

```

conn.tcp conn: -72228

done..

XILSOCK TCP ACK

Connection 1 added

XILSOCK TCP DATA

Set LEDs...

Your input is: 12.

mul1: 12

mul2: 4

mul1 * mul2 = : 48

Send on socket: 1

conn.tcp conn: -72228

XILSOCK TCP ACK

Connection 1 added

XILSOCK TCP DATA

Set LEDs...

Your input is: 0.

mul1: 0

mul2: 4

mul1 * mul2 = : 0

Send on socket: 1

conn.tcp conn: -72228

done..

XILSOCK TCP ACK

Connection 1 added

XILSOCK TCP DATA

Set LEDs...

Your input is: 3.

mul1: 3

mul2: 4

mul1 * mul2 = : 12

Send on socket: 1

conn.tcp conn: -72228

done..

XILSOCK TCP ACK

```

# 2.3 Conclusion

This chapter provides background information of the Virtex-II Pro development system. The sample design demonstrates how an embedded application can be implemented using the Xilinx EDK. This design can be served as a laboratory experiment, since its complexity would give students a chance to learn the Xilinx EDK and design a small yet complex embedded application that uses one of the two embedded cores and the FPGA. The Xilinx EDK and the Virtex-II Pro development system together provide engineers with a flexible embedded application development environment. We

can attach new HDL components to meet design requirements. This feature allows us to easily add and remove devices in an operating system, which will be shown in Chapter 4.

### CHAPTER THREE

### DISTRIBUTED SYSTEM V.S. SHARED MEMORY SYSTEM

# 3.1 Parallel Computing

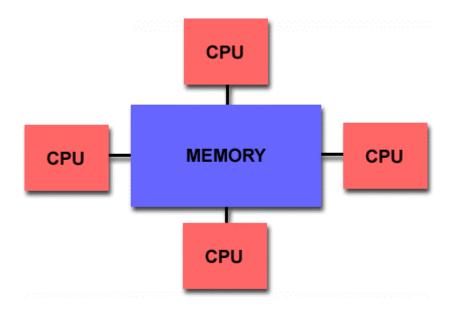

Traditionally, a computer solves problems by executing a series of instructions in a processor, and only one instruction can be executed at a time. Parallel computing in short refers to more than one processors running simultaneously to solve one problem. It is a method to speed up computation. We can have all processors run the same instructions. We can also split a task into smaller sub-tasks, and assign each processor some sub-tasks. These processors are running in parallel to solve the computational problem. Parallel computing is an ideal solution for systems that have interrelated events happening at the same time, require complex numerical simulations, or process a large amount of data. Examples of parallel computing systems include weather patterns, automobile assembly line, manufacturing processes, web search engines, corporation managements, etc. Memory architectures for parallel computing can be classified into three categories [8]:

# **Shared Memory**

Processors share the same memory resources. This is often seen in a computer with multiple processors. Changes made by a processor in the shared memory region must be visible to all other processors. Because we have two processors in the Virtex-II Pro FPGA, and we are free to use available memory on the board, a shared memory system can be built in this particular platform.

Figure 3.1: Shared memory system

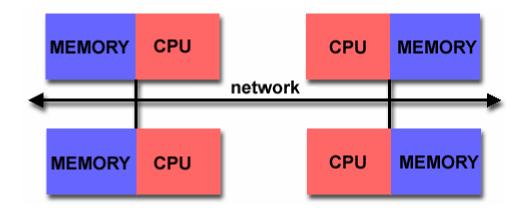

# **Distributed Memory**

Multiple processors are running in a network, but appear to a user as a single system. Each processor has its own local memory and operates independently. Changes in the local memory do not have effects in the memory of other processors. If a processor needs to access data in other processors, a communication link must be established. An example of distributed system would be an automatic banking system. Any machine in the system must be informed when a transaction occurs to an account. The system looks like one computer to a user, but in fact many machines are running together to maintain bank accounts. It is possible to establish a distributed system using the Virtex-II Pro development systems. Each processor can perform independent work, and share resources through a communication protocol. Because we have Ethernet available on the board, networking can be used for inter-communication.

Figure 3.2: Distributed memory system

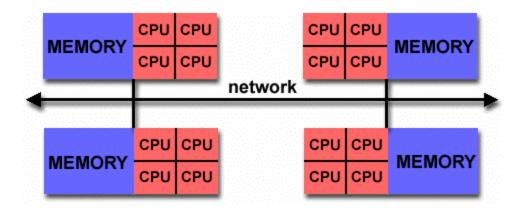

# **Hybrid Distributed-Shared Memory**

This architecture combines the above two. This type of architecture can be seen in a network of Symmetric Multiprocessing (SMP) machines. Each SMP machine has shared memory, usually the cache areas. To communicate with other SMP machines, the distributed memory architecture is used. For the purpose of this research, the hybrid distributed-shared memory system will not be further discussed.

Figure 3.3: Hybrid distributed-shared memory system

# 3.2 Using Dual PowerPC Core

Since the Virtex-II Pro FPGA has two PowerPC processors, we will want to be able to build a shared memory system. Because the Virtex-II Pro FPGA uses the IBM CoreConnect bus architecture, building a shared memory system for PowerPC405 cores can be done in Platform Studio.

# 3.2.1 A Simple Shared-Memory System

To demonstrate how a shared memory system can be built on the Virtex-II Pro development system, the following design has been implemented. Since the standalone operating system does not provide any synchronization mechanism and the hardware does not implement cache coherence, an engineer has to handle related issues in the software program. The focus here will be on how to build a shared memory system and how to access shared data.

# **Shared Memory System Design**

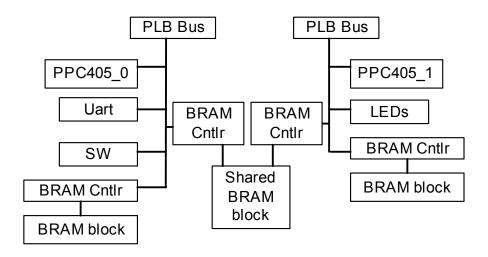

Each PowerPC processor has its own block RAM (BRAM). There is also a block of shared memory for the two processors. Shared data is stored in the shared BRAM region. PPC0 monitors the status of switches, and PPC1 controls the status of LEDs. PPC0 receives a user input from the switches, and PPC1 displays the corresponding value on the LEDs. A UART is attached to PPC0 to display current shared data. PPC0 also displays a counter variable changed by PPC1. The following shows the block diagram of the shared memory system.

Figure 3.4: Shared memory system block diagram

# **Shared Memory Implementation**

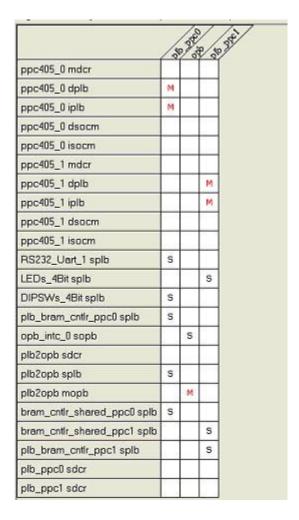

Because the Xilinx EDK does not particularly support dual core designs, there is a need to manually set up the system. The following figures show the bus connections and BRAM port connections:

Figure 3.5: Bus connections for the shared memory system

| Cntir Port                   | BRAM Port         |   | Connector             |

|------------------------------|-------------------|---|-----------------------|

| plb_bram_cntlr_ppc0 porta    | bram_ppc0 PORTA   | ~ | plb_bram_ppc0_porta   |

| bram_cnttr_shared_ppc0 porta | bram_shared PORTA |   | bram_shared_ppc0_port |

| bram_cnttr_shared_ppc1 porta | bram_shared PORTB | • | bram_shared_ppc1_port |

| plb_bram_cnttr_ppc1 porta    | bram_ppc1PORTA    | v | plb_bram_ppc1_porta   |

Figure 3.6: BRAM ports connected to the controller ports

As shown in the figure, both UART and switches are connected to PPC0 as PLB slave devices, and LEDs are connected to PPC1 as a PLB slave device. Each processor has two BRAM controllers: one for the local BRAM, and the other for the shared BRAM. The screenshot shown below displays the address map of the shared memory system:

| Instance               | Prefix | Base Address | High Ad    | Size  |   | Min Size |  |

|------------------------|--------|--------------|------------|-------|---|----------|--|

| ppc405_0               | ISOCM  |              |            | UNS   | * | 4        |  |

| ppc405_0               | DSOCM  |              |            | UNS   | • | 4        |  |

| ppc405_1               | ISOCM  |              |            | UNS   | • | 4        |  |

| ppc405_1               | DSOCM  |              |            | UNS   | * | 4        |  |

| plb_ppc0               |        |              |            | UNS   | • | 8        |  |

| RS232_Uart_1           |        | 0x80200000   | 0x8020ffff | 64 KB | * | 0x2000   |  |

| LEDs_4Bit              |        | 0x80000000   | 0x8000ffff | 64 KB | * | 0x200    |  |

| DIPSWs_4Bit            |        | 0x80020000   | 0x8002ffff | 64 KB | • | 0x200    |  |

| plb_bram_cnttr_ppc0    |        | 0xfffe0000   | 0xfffeffff | 64 KB | * | 0x4000   |  |

| opb_intc_0             |        | 0x41200000   | 0x4120ffff | 64 KB | • | 0x20     |  |

| opb                    |        |              |            | UNS   | * | 0x200    |  |

| plb2opb                | RNG0   | 0x41200000   | 0x4120ffff | 64 KB | * | 0        |  |

| plb2opb                | RNG1   |              |            | UNS   | * | 0        |  |

| plb2opb                | RNG2   |              |            | UNS   | * | 0        |  |

| plb2opb                | RNG3   |              |            | UNS   | ¥ | 0        |  |

| plb2opb                | DCR    |              |            | UNS   | * | 0        |  |

| bram_cntlr_shared_ppc0 |        | 0xfffd0000   | 0xfffdfff  | 64 KB | * | 0x4000   |  |

| bram_cntlr_shared_ppc1 |        | 0xfffd0000   | 0xfffdfff  | 64 KB | * | 0x4000   |  |

| plb_bram_cnttr_ppc1    |        | 0xffff0000   | 0×fffffff  | 64 KB | + | 0x4000   |  |

| nh nnc1                |        |              |            | LINS  | - | 8        |  |

Figure 3.7: Address Map

Internal ports identical to PPC0 for PPC1 need to be added. Clock and reset ports also need to be added for PLB and BRAM controller connected to PPC1. The following figures show the newly added internal port connections. The prefix "ppc\_1\_" for C405RSTCHIPRESETREQ, C405RSTCORERESETREQ, and C405RSTSYSRESETREQ has been added, because the Xilinx EDK does not allow multiple drivers on these ports. Parameters for each core need to match one another. This is the last step in building a dual-core system.

| ppc405_1 | CPMC405CLOCK        | proc_ck_s                | ~ | 1 | CLK  |

|----------|---------------------|--------------------------|---|---|------|

| ppc405_1 | PLBCLK              | sys_clk_s                | • | 1 | CLK  |

| ppc405_1 | C405RSTCHIPRESETREQ | ppc1_C405RSTCHIPRESETREQ | * | 0 |      |

| ppc405_1 | C405RSTCORERESETREQ | ppc_1C405RSTCORERESETREQ | * | 0 |      |

| ppc405_1 | C405RSTSYSRESETREQ  | ppc1_C405RSTSYSRESETREQ  | - | 0 |      |

| ppc405_1 | RSTC405RESETCHIP    | RSTC405RESETCHIP         | - | I |      |

| ppc405_1 | RSTC405RESETCORE    | RSTC405RESETCORE         | • | 1 |      |

| ppc405_1 | RSTC405RESETSYS     | RSTC405RESETSYS          | * | I |      |

| ppc405_1 | EICC405EXTINPUTIRQ  | EICC405EXTINPUTIRQ       | - | 1 | INTE |

Figure 3.8: Ports for PPC1

| plb_bram_cnttr_ppc1 | plb_clk | sys_dk_s      | <u>*</u> 1 | CLK |

|---------------------|---------|---------------|------------|-----|

| plb_ppc0            | SYS_Rst | sys_bus_reset | <u>-</u> 1 |     |

| plb_ppc0            | PLB_Ck  | sys_dk_s      | <u>-</u> 1 | CLK |

| opb                 | SYS_Rst | sys_bus_reset | <u>*</u> 1 |     |

| opb                 | OPB_Clk | sys_dk_s      | <u>*</u> I | CLK |

| plb_ppc1            | PLB_Ck  | sys_dk_s      | <u>-</u> 1 | CLK |

| plb_ppc1            | SYS_Rst | sys_bus_reset | <u> </u>   |     |

Figure 3.9: Added ports for PLB and BRAM controller connected to PPC1

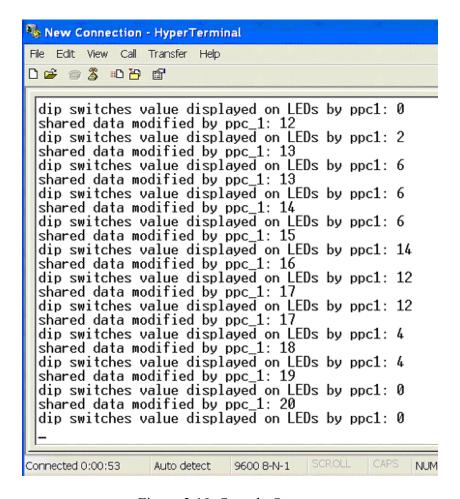

Once the hardware system is built, the system can be tested with a sample application. The software code for PPC0 reads the switch input from a user and stores the value into a shared memory location. PPC1 reads the value from the shared memory location and displays it to LEDs. PPC1 also modifies a counter variable in another shared memory location and lets PPC0 display the updates in the terminal. The source code can be found in Appendix B. The following figure is a screenshot of sample outputs:

Figure 3.10: Sample Outputs

The above design shows how a shared memory system can be implemented in the Virtex-II Pro development system. There are other ways to design a dual-core system. However, the above experiment shows the fundamental ideas. One important note regarding dual core designs on the PowerPC cores: Because the PowerPC405 cores do not implement cache coherence, it is not feasible to build a symmetric multiprocessing system under Linux. This will be further discussed in the embedded Linux port section. At the time this experiment was done, Xilinx did not offer support of any kind on using both PowerPC cores in the Virtex-II Pro FPGA. The current solution is to build one manually in a standalone operating system as described above.

## 3.3 The Virtex-II Pro Distributed System

As mentioned before, we can use Ethernet to set up a Virtex-II Pro distributed system. Using the shared memory architecture in an operating system for the PowerPC405 cores is not feasible at this time. As a result, the development platform is not a good choice to build shared memory applications under an embedded operating system. But it is an excellent solution as a distributed system. We can have each board complete tasks using the FPGA and processors co-design feature. The data can be shared among all computing components within the distributed system. There will be a lot of factors to consider before we can design an efficient and fault tolerant distributed system. The topic will not be further discussed here, as it is not within the scope of this research, and worse more hardware to do distributed system experiments is not available.

### 3.4 Conclusion

This chapter explores the capability of parallel computing on the Virtex-II Pro development system. As a result, we are able to build a parallel computing system in the standalone environment, even though the Xilinx EDK does not specifically offer this feature. Because the onboard PowerPC processors do not implement cache coherence, applications that can be built on the development system are limited. The chapter is also part of the preliminary work of the embedded Linux port, as the possibility of extending the Linux port to the second PowerPC processor will be investigated.

#### **CHAPTER FOUR**

### EMBEDDED LINUX ON THE VIRTEX-II PRO SYSTEM

### 4.1 Background

Most embedded applications require the system to handle multiple concurrent processes. An embedded system without an operating system does not offer this capability. For example, if we want a process that gathers information in a field and another process monitoring errors, we will need to combine them into one application. A kernel offers services such as schedulers, synchronization mechanisms, and threads, which give programmers great flexibility in designing complex embedded applications [9]. With the services an operating system provides, we can have many independent processes running in a system. Inter-process communication can be done using shared memory, synchronization, remote procedure calls, or message passing, depending on the operating system design and the programmer's decision. Operating systems on embedded systems are usually designed with the real-time response feature. Most embedded applications have time constraints, so embedded applications within a real-time operating system (RTOS) gives us a more reliable system. Given the advantages of having an operating system, we explore the possibilities of installing one on the Virtex-II Pro development system, preferable a real-time operating system.

### 4.2 Embedded Linux on the Virtex-II Pro Development System

The Xilinx EDK provides several options: Xilkernel, VxWorks, and MontaVista Linux. Xilkernel is a robust and modular kernel that is highly integrated with the Platform Studio framework [3]. It comes with a licensed EDK. It provides a Portable

Operating System for Unix (POSIX) interface to the kernel, and supports core features for a real-time embedded kernel such as schedulers, synchronization services, and interprocess communication services. The main disadvantage of Xilkernel is that it is specific to certain Xilinx FPGAs and can only be invoked in the Platform Studio. It does not provide the flexibility as a general purpose embedded operating system. MontaVista Linux and VxWorks both require licensed development packages. These commercial products provide ready-to-use cross compiling tools, and custom Unix-based operating systems. As researchers, we will want to be able to use open sources for obvious reasons.

Linux has been a popular choice in the embedded system world for several reasons:

- Open Source and Royalty Free: Anyone can obtain the source and make modifications to fit specific design requirements.

- Small in Size: The kernel image of an embedded Linux is usually about 2MB to 8MB.

- Stable and Well-Supported Operating System: Linux has over ten years of development history, and has been used in many hi-tech products. It supports most processor architectures and devices.

In order to find out whether embedded Linux is suitable for the Virtex-II Pro development system, more factors need to be considered and examined.

As we all know, Linux supports most desktop computers. However, every device is unique to a particular embedded system. Therefore, an embedded Linux system normally requires custom drivers support. Montavista has partnered with Xilinx, and has developed commercial embedded Linux kits for some Xilinx platforms. Although the

complete kit requires licensing, the device drivers are under General Public License (GPL). Even though these drivers are generic and might not work on different Xilinx platforms, we can modify the source code to adapt devices on the Virtex-II Pro development system. This advantage enables us to bring up the peripherals on the board without spending time developing drivers. We can also add the Board Support Package (BSP) for the Virtex-II Pro development system to the Linux kernel, which contains development platform specific device drivers

The Virtex-II Pro FPGA allows custom processor peripherals. We can easily access these custom peripherals in the standalone operating system. However, with the loadable module feature of Linux, we can decide whether to build the drivers in the kernel or to load these modules dynamically [9]. This feature allows us to load a device at run-time, which we will need in some embedded systems. For example, we might want the system to reload a backup device when the current device fails at any time. Embedded system tasks are critical, and this feature brings us a more stable system.

Embedded Linux is configured to fit small systems. It can be viewed as a stripped version of standard Linux. In order to handle critical tasks, a real-time scheduler and preemptive kernel are added to embedded Linux. We can write embedded applications using built-in threads packages once we have the embedded Linux running. Based on all the above factors, embedded Linux is ideal for the Virtex-II Pro development system.

### 4.3 Requirements for the Linux Port

Port of Linux to an embedded system is not as simple as the desktop installation. Embedded systems have limited resources, and usually do not have enough space to run a compiler. Even if we have sufficient disk space to hold a compiler, we will have poor performance out of the slow compiler. For this reason, most people choose to compile source code in a host machine, and then download binaries to the target system. If the host computer is not a PowerPC machine, a cross compiler needs to be built. Because embedded platforms are hardware specific, we will need a suitable kernel. At the time the research is conducted, several companies have developed Virtex-II Pro FPGA compatible kernels. Among all, only MontaVista has released an open source kernel (2.4.x) with the support. The newest kernel at this time is 2.6, but the support for this specific FPGA is removed from 2.5 and above. Therefore, 2.4.x seems to be the only open source that can be used for the port. Other than the kernel and compiler, we will also need a root filesystem and BSP. The following lists the requirements for the Linux port:

### **Linux Kernel**

MontaVista offers an open Linux kernel 2.4.x that supports ML300 boards. The ML300 boards use the Virtex-II Pro FPGA series same as our development system. Even though the kernel is specific to the ML300 board, its support for the Virtex-II Pro FPGAs can be used on our development system.

## **Board Support Package (BSP)**

The BSP allows us to access devices specific to this platform. Because MontaVista supports Linux, we can use their BSP that comes with the Xilinx EDK.

### Crosstool

The target build is a PowerPC processor. Since the development host machine available is not a PowerPC machine, a cross compiler is needed to compile source code to PowerPC machine code. It is a cumbersome process to build a cross

compiler. We will need to build GNU Binutils, which contains a linker, assembler, and other binary tools. We then install Glibc, the GNU C library. The last step is to build the Gcc compiler. It takes a lot of time and patience to have everything correctly configured and properly installed. Fortunately, Dan Kegel [10] has developed Crosstool, which provides a set of useful shell scripts that does all the work for us. The scripts will download tools for you if they are not found in the host machine. It takes about two hours on a Pentium 4 machine to build a cross compiler using Crosstool.

### Compatible GCC and Glibc

Crosstool needs to be built with certain Gcc and Glibc combinations. If the Gcc and Glibc combination on the host machine is not supported, they need to be updated.

## **Root Filesystem**

We will need a root filesystem in Linux to do meaningful work. The filesystem contains startup files, utilities, and file systems. BusyBox combines tiny versions of many common Unix utilities into a single small executable [11], and will be used to create the root filesystem.

## **Base System**

The base system contains hardware specifications for the embedded system.

## **System Advanced Configuration Environment (ACE) File**

System ACE files provide an easy way to program the FPGA. The system ACE controller allows us to boot from a CompactFlash.

## CompactFlash Card

Both the kernel and the root filesystem will be stored in the CompactFlash card.

# 4.4 Porting Linux

Thanks to the pioneer work done at BYU [12] and by Wolfgang Klingauf [13], good documentation on porting Linux for some Xilinx platforms can be found across the Internet. This section shows the steps for the Linux port.

## Hardware and Software Specifications

### Hardware:

- Sony VAIO with a Pentium 4 processor for Debian

- Pentium III 1.0 GHz for Windows XP

- Xilinx Virtex-II Pro Development System

- Compact Flash Memory Card (512MB) and Reader

- Kingston 256MB Memory

- Serial Cable for Standard Input/Output

- USB Cable

## **Software:**

- Xilinx EDK7.1.2 SP2

- RedHat 9 Shrike & Debian 3.1 Sarge (either one can be used)

- Crosstool 0.38

- BusyBox 1.1.0

- TeraTerm Pro 3.1

# **Building A Cross Compiler**

A cross compiler is built on a Pentium 4 machine using Crosstool.

## Obtaining the Linux Source

The kernel source for this research is downloaded from MontaVista and has a version number of 2.4.25.

## Configuring the Kernel

For this Linux port, the kernel configuration contains the following settings:

## **Code Maturity Level Options**

Prompt for development and/or incomplete drivers

## **Loadable Module Support**

Enable loadable module support

# **Platform Support**

40x Processor Type

Xilinx-ML300 Machine Type

Math emulation

<UART0> TTYS0 device and default console

UART0

# **General Setup**

Networking support

Sysctl support

System V IPC

Default bootloader kernel arguments

"console=ttyS0,9600 root=/dev/xsysace/disc0/part3 rw"

## **Memory Technology Devices (MTD)**

Memory Technology Device (MTD) Support

MTD partitioning support

RedBoot partition table parsing

Direct char device access to MTD devices

Caching block device access to MTD devices

RAM/ROM flash chip device drivers

Detect flash chips by Common Flash Interface (CFI) probe

Support for AMD/Fujitsu flash chips

### **Block Devices**

Xilinx on-chip System ACE

Loopback device support

Network block device support

RAM disk support

(4096) Default RAM disk size

Initial RAM disk (initrd) support

# **Networking Options**

**Socket Filtering**

Unix domain sockets

TCP/IP networking

IP: multicasting

IP: kernel level autoconfiguration

IP: DHCP support

IP: TCP syncookie support (disabled per default)

## **Network Device Support**

Network device support

Ethernet (10 or 100Mbit)

Xilinx on-chip ethernet

### **Character devices**

Standard/generic (8250/16550 and compatible UARTs) serial support

Support for console on serial port

Unix98 PTY support

## File systems

Journaling Flash File System v2 (JFFS2) support

JFFS2 debugging verbosity (0=quiet, 2=noisy)

Virtual memory file system support (former shm fs)

/proc file system support

/dev file system support (EXPERIMENTAL)

Automatically mount at boot

/dev/pts file system for Unix98 PTY

Second extended fs support

Native Language Support

Default NLS Option: "iso8859-1"

# Kernel hacking

Kernel debugging

Include BDI-2000 user context switcher

Add any additional compile options

Additional compile arguments: "-g -ggdb"

## (0) Kernel messages buffer length shift (0=default)

The above kernel services are chosen to fit this particular system. This configuration contains a minimal working kernel. The kernel can always be re-compiled with more options, if more services are required.

## Building a Base System

A base system that has the following components has been built using the Xilinx Platform Studio.

- PowerPC at 300MHz

- RS232\_Uart\_1: Peripheral OPB UART 16550, Configure as UART 16550, and use Interrupt

- Ethernet MAC: Peripheral OPB ETHERNET, No DMA, and use Interrupt

- SysACE\_CompactFlash: Peripheral OPB SYSACE, and use Interrupt

- DDR\_256MB\_32MX64\_rank1\_row13\_col10\_cl2\_5: Peripheral PLB

DDR, and use Interrupt

- PLB BRAM IF CNTLR: Memory Size 128KB

After downloading a bitstream to an FPGA, the processor comes out of the reset state and starts executing. If no application is initialized, the processor might execute random code and get in some state that it cannot be brought out of with a soft reset [3]. XPS provides a bootloop program that keeps the processor in a defined state until an application is ready to run. We will need a bootloop to keep the PowerPC processor defined prior the kernel startup. To use the bootloop, set ppc405\_0 bootloop to initialize BRAMs, and create a downloadable bitstream for the system.

## Generating BSP

The following parameters are set in the Software Platform Settings window.

- linux mvl31 version 1.0.1a as the operating system for ppc405 0.

- MEM SIZE: 0x10000000

- PLB CLOCK FREQUENCY: 100000000

- TARGET DIR: 'C:/XUPV2P/temp'

- connected\_peripherals: RS232\_Uart\_1, Ethernet\_MAC,

SysACE CompactFlash, opb\_intc\_0

BSPs are generated by Libgen. Once Libgen is done, BSPs can be found in the target directory.

# Compiling the Kernel

Once the kernel is compiled with no errors, the kernel image zImage.elf is stored in the arch/ppc/boot/images directory.

## Creating an ACE file

The genace.tcl file contains several board configurations. The parameters for the Virtex-II Pro development system need to be manually added. ACE files are generated by issuing proper commands in the Xilinx Cygwin shell.

## Creating a Root File System

There are different ways to locate a root filesystem. The CompactFlash card can be partitioned to store the root filesystem. This way, the CompactFlash card can simply be inserted and have the hardware do the rest.

Wolfgang Klingauf provides a very useful script to make a root filesystem using BusyBox. BusyBox combines tiny versions of many common Unix utilities into a single

small executable. A root filesystem is made with proper options using Klingauf's scripts for this Linux port.

### Moving Everything to the CompactFlash

The CompactFlash needs to be divided into three partitions. The following shows the partition table:

Partition 1: FAT16 (6)

Partition 2: Linux Swap Partition (82)

Partition 3: Linux (83)

Partition 3 is where the root filesystem is stored. The FAT partition needs a particular format under Windows [4]. The ACE file is copied to this partition.

## Running Linux

The Linux port is now completed. The following is the log of Linux running on the Virtex-II Pro development system:

```

00400000 004A01E4

loaded at:

board data at: 0049D13C 0049D154

relocated to: 00405634 0040564C

zimage at: 00405B39 0049C3B3 avail ram: 004A1000 10000000

Linux/PPC load: console=ttyS0,9600 root=/dev/xsysace/disc0/part3 rw

Uncompressing Linux...done.

Now booting the kernel

Linux version 2.4.25 (root@jabu-01) (gcc version 3.4.1) #45 Thu Feb 23

10:50:40

PST 2006

Xilinx Virtex-II Pro port (C) 2002 MontaVista Software, Inc.

(source@mvista.com)

On node 0 totalpages: 65536

zone(0): 65536 pages.

zone(1): 0 pages.

zone(2): 0 pages.

Kernel command line: console=ttyS0,9600 root=/dev/xsysace/disc0/part3

Xilinx INTC #0 at 0x41200000 mapped to 0xFDFFE000

Calibrating delay loop... 299.82 BogoMIPS

Memory: 257620k available (1068k kernel code, 308k data, 60k init, 0k

highmem)

Dentry cache hash table entries: 32768 (order: 6, 262144 bytes)

```

```

Inode cache hash table entries: 16384 (order: 5, 131072 bytes)

Mount cache hash table entries: 512 (order: 0, 4096 bytes)

Buffer cache hash table entries: 16384 (order: 4, 65536 bytes)

Page-cache hash table entries: 65536 (order: 6, 262144 bytes)

POSIX conformance testing by UNIFIX

Linux NET4.0 for Linux 2.4

Based upon Swansea University Computer Society NET3.039

Initializing RT netlink socket

Starting kswapd

devfs: v1.12c (20020818) Richard Gooch (rgooch@atnf.csiro.au)

devfs: boot options: 0x1

JFFS2 version 2.2. (C) 2001-2003 Red Hat, Inc.

pty: 256 Unix98 ptys configured

Serial driver version 5.05c (2001-07-08) with no serial options enabled

ttyS00 at 0xfdfff003 (irq = 29) is a 16550A

RAMDISK driver initialized: 16 RAM disks of 4096K size 1024 blocksize

loop: loaded (max 8 devices)

Partition check:

xsysacea: p1 p2 p3

System ACE at 0x41800000 mapped to 0xD1000000, irq=30, 500976KB

eth0: using fifo mode.

eth0: No PHY detected. Assuming a PHY at address 0.

eth0: Xilinx EMAC #0 at 0x40C00000 mapped to 0xD1013000, irq=31

eth0: id 2.0h; block id 7, type 1

NET4: Linux TCP/IP 1.0 for NET4.0

IP Protocols: ICMP, UDP, TCP, IGMP

IP: routing cache hash table of 2048 buckets, 16Kbytes

TCP: Hash tables configured (established 16384 bind 32768)

NET4: Unix domain sockets 1.0/SMP for Linux NET4.0.

EXT2-fs warning: mounting unchecked fs, running e2fsck is recommended

VFS: Mounted root (ext2 filesystem).

Mounted devfs on /dev

Freeing unused kernel memory: 60k init

Welcome to ML300 powerpc linux 2.4.21, E.I.S. edition

Starting system...

mounting /proc: done.

Mounting '/' read-write: done.

brining up loopback interface: done.

Mounting /tmp: done.

Starting syslogd: done.

Starting klogd: done.

Starting inetd: done.

System started.

ML300 powerpc linux 2.4.21-pre7 E.I.S. edition

(none) login: root

Welcome to the ML300, EIS edition

Be careful, it's blue.

```

BusyBox v1.1.0 (2006.01.17-20:03+0000) Built-in shell (ash) Enter 'help' for a list of built-in commands.

```

# cd /

# ls

lib

modules0201 root

a.out

dev

usr

bin

etc

linuxrc

opt

sbin

var

boot

home

mnt

proc

tmp

```

## 4.5 Comments on Symmetric Multiprocessing

Once Linux is ported to the board, the next thing we want to do is to enable Symmetric Multiprocessing (SMP). SMP allows multiple processors to complete their own tasks simultaneously. It uses one operating system and shares common resources among processors. Unfortunately, due to the hardware architecture of PowerPC405 cores, SMP is not feasible. The PowerPC405 cores do not define the size, structure, replacement algorithm, or mechanism used for maintaining cache coherency [4], which is what we need in a multiprocessing environment. It is possible to implement cache coherence in software. However, it is an expensive process, as the software program will have to track all memory accesses in all processors. This is an in-deterministic process and will sacrifice timeliness for hard real-time applications. Cache coherence is rarely done in software. As for the PowerPC405 cores, no one has enabled SMP at this point. One way to enable both cores is to have a copy of operating system running in each processor. Mind, a Belgian company, has managed to do this in Linux for the Virtex-II Pro FPGA. This approach is not studied any further in this research, because it is not considered as a shared memory multiprocessor system.

### **4.6 Linux Device Drivers**

Once we have an operating system running on the board, we will want to run applications in the OS. Most embedded applications require interactions with hardware devices. Because MontaVista only offers a limited number of generic drivers for the

Virtex-II Pro platforms, we will need to write custom device drivers for our designs. Unix classifies devices into three types [14]: character module, block module, and network module. There are two ways to build a Linux device driver namely: (i) build in as part of the kernel source, and (ii) create a loadable module. The former requires kernel recompilation each time you modify the driver source. The latter provides more flexibility as you load the module while the kernel is running. This section provides two sample driver designs for research completeness. A character device can be accessed as a file, which is ideal for implementing device IOs. The first module does the work in kernel, without any user application support. The second module gets loaded into the kernel, and a user application interfaces the module to perform desired IOs.

### 4.6.1 Loadable Kernel Module

This module reads and writes a register in the FPGA. A custom IP with one software accessible register is created. The user logic VHDL code is generated by EDK, which performs read and write operations. In the kernel module code, a write is issued and then a read. After the data is written out, the data value is changed to some other number. This ensures the data read in later is correct. The code is compiled using the Makefile. The output binary (.o) is loaded into the kernel with the command "insmod io driver.o". The following is a screenshot of the output:

```

Tera Term Web 3.1 - COM1 VT

File Edit Setup Web Control Window Help

# cd iodrive/

# ls

io_driver.o

# 1smod

Module

Size Used by

Not tainted

# insmod io_driver.o

ioremap: Virtual Address d1028000

Physical Address 11028000

Data to write out: 0000000a

Change io_reg to: 00000005

Read register value into io_reg: 0000000a

# 1smod

Module

Size

Used by

Not tainted

io driver

912

0 (unused)

# rmmod io_driver

Release Memory Region...

```

Figure 4.1: Loadable module output

The source code for the driver can be found in Appendix C.

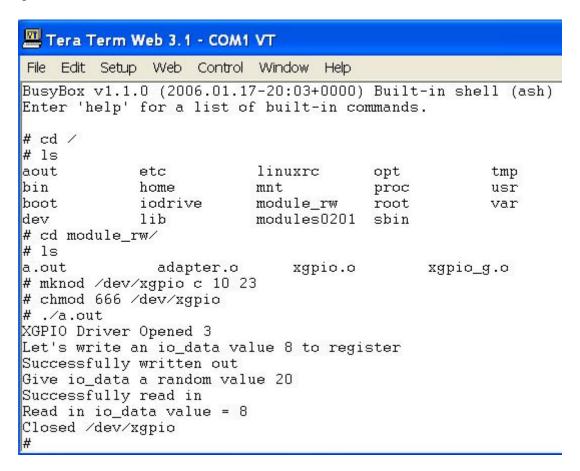

### 4.6.2 Loadable Kernel Module with User Programs

The above module works well for the system, however, we will eventually want to access hardware from a user program. We can make drivers to support user programs. One way to enter the kernel mode from user mode in Linux is through system calls. Two kernel routines copy\_from\_user() and copy\_to\_user() are needed for data transfer from/to the user space. This design performs the same function as above, except that we can now modify the value of the register in a user application.

In this design, we can access the hardware same as the way we access a file in a user program, meaning we can use open(), close(), read(), and write() function calls. This module works as a loadable module and as a built-in module.

After the module is loaded successfully, a special file that has the same name as the file in the user program needs to be created. In this case, such a file is created with the command "mknod /dev/xgpio c 10 23", where "c" indicates it is a character device, 10 is the major number for misc devices, and 23 is the minor number assigned to the device. The permission of the file also needs to be changed: "chmod 666 /dev/xgpio". The program can be tested by executing the binary. The following is a screenshot of the output:

Figure 4.2: Enhanced loadable module output

The source code for the driver can be found in Appendix D.

## 4.7 Conclusion

An embedded system with an operating system offers more flexibility to embedded applications. An embedded Linux operating system has been ported to one PowerPC processor on the Virtex-II Pro development system successfully. The Xilinx EDK allows us to add and remove built-in and custom IP cores. We can now modify devices within the operating system by loading/un-loading proper device drivers. This feature is particularly useful when we want to load a device at run time, which is required for some embedded applications. Although Symmetric Multiprocessing can not be achieved on this development platform, the research effort provides the insight, which suggests an alternative approach or a new hardware development.

#### **CHAPTER FIVE**

### HARDWARE SOFTWARE PARTITIONING

### 5.1 Background

The FPGA and embedded processors co-existence feature of the Virtex-II Pro FPGA enables us to design embedded applications that take the advantage of hardware software partitioning. The problem of hardware software partitioning has seen over a decade of activity and some of the notable work includes that presented in [15, 16]. This problem has been made easy by the development of logic systems with embedded cores. It is not our desire to design algorithms to exploit these benefits. In simple terms hardware software partition involves being able to identify an application's components that can be better performed in hardware and those that can be better performed in software, and dividing them to compute in their respective units (Hardware or Software). In this study no algorithm has been used to identify the respective tasks since efforts are focused on presenting a diverse design environment that offers computational efficiency along with the flexibility of a real-time kernel. A simple digital Finite Impulse Response (FIR) filter has been used to demonstrate the hardware software co-design as well as the computational efficiency gained. Partitioning of this FIR filter is done manually and is not as cumbersome to manage.

As mentioned already, we can move tasks that can be done efficiently in the hardware (FPGA) to obtain better performance of an application. An example of such would be to move the multiply-and-accumulate part of the FIR filter to the FPGA for fast computation, as this takes much longer in the PowerPC processors. The memory

management and switching of coefficients will be left as software tasks. This chapter shows how hardware software partitioning can be done in the Virtex-II Pro development system, as well as the performance comparison between a case with and one without hardware software partitioning systems and its significance. An audio filtering application will be designed, and the finite impulse response filter is chosen for its compute intensive feature.

### 5.1.1 Digital Signal Processing

Digital signal processing provides probably some of the most compute intensive applications in engineering. The Virtex-II Pro development system is not intended for digital signal processing, but it has such powerful computational capabilities and digital signal processing applications have computational needs that can be met using this system. In order to experiment hardware and software partitioning, real-time processing and other related aspects of real-time systems design; adaptive filtering has been considered. Finite impulse response filters have been used to demonstrate these important embedded systems design issues on the Virtex-II Pro development system. In the following a brief on two types of digital filters is presented.

## **5.2 FIR Filter Design**

Finite impulse response (FIR) filters are one of two primary types of digital filters used in Digital Signal Processing (DSP) applications the other type being infinite impulse response (IIR). IIR filters use feedback and each type of filter has advantages and disadvantages [17, 18]. Overall, though, the advantages of FIR filters outweigh the disadvantages as a result they are used much more than IIR filters. The FIR filters offer the following advantages:

- They can easily be designed to have a linear phase, in other words they delay the input signal, but do not distort its phase.

- They are simple to implement and on most DSP microprocessors the computations can be done by looping a single instruction.

- They are easy to manipulate allowing decimation (reducing the sampling rate), interpolation (increasing the sampling rate), or both.

- Whether decimating or interpolating, the use of FIR filters allows some of the calculations to be omitted, thus providing an important computational efficiency.

Coefficient symmetry also saves memory space.

- They have desirable numeric properties. In practice, all DSP filters must be implemented using "finite-precision" arithmetic, that is, a limited number of bits. The use of finite-precision arithmetic in IIR filters can cause significant problems due to the use of feedback, but FIR filters have no feedback, so they can usually be implemented using fewer bits, and the designer has fewer practical problems to solve related to non-ideal arithmetic.

- They can be implemented using fractional arithmetic. Unlike IIR filters, it is always possible to implement a FIR filter using coefficients with magnitude of less than 1.0. (The overall gain of the FIR filter can be adjusted at its output, if desired).