## DESIGN OF A NEW TRANSFORMER ISOLATED ANALOG ACQUISITION SYSTEM HAVING GREATLY REDUCED TRANSFORMER SIZE AND WEIGHT WHILE ACHIEVING HIGH ACCURACY

By

### TIMOTHY MICHAEL MINTEER

A thesis submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

WASHINGTON STATE UNIVERSITY School of Electrical Engineering and Computer Science

May 2008

To the Faculty of Washington State University:

The members of the Committee appointed to examine the thesis of TIMOTHY MICHAEL MINTEER find it satisfactory and recommend that it be accepted.

Chair

#### ACKNOWLEDGMENT

I would like to thank Schweitzer Engineering Labs, Inc., and in particular, Doug Trout, for their support of the design, implementation, and prototype testing of this new isolated analog acquisition system. I would also like to thank my advisor, Dr. Robert Olsen, for his support, review, and encouragement of this work. Also, a big thanks to Dr. Sandip Roy and Dr. John Schneider for assistance and for serving on my committee.

# DESIGN OF A NEW TRANSFORMER ISOLATED ANALOG ACQUISITION SYSTEM HAVING GREATLY REDUCED TRANSFORMER SIZE AND WEIGHT WHILE ACHIEVING HIGH ACCURACY

Abstract

by Timothy Michael Minteer, M.S. Washington State University May 2008

Chair: Robert G. Olsen

The design of a new transformer isolated analog acquisition system greatly reduces the size, weight, and cost of the isolation transformer. The concept of pulsing the isolated analog signal only for the portion of time needed for A-D conversion is developed. High accuracy of the isolated analog signal is achieved using an operational amplifier with a feedback winding from the isolation transformer. The additional use of the isolation transformer for an isolated switched mode power supply is also developed. The implementation of the isolation transformer using a small E-E ferrite core and printed circuit windings is described.

A SPICE (Simulation Program with Integrated Circuit Emphasis) model is developed for the E-E ferrite core, printed circuit board winding transformer used in the Isolated Analog Selector circuit. SPICE models for the part-to-part and temperature extreme variations identify the design constraints of the isolation transformer. SPICE models of the electronic control circuitry used in the new isolated analog acquisition system help identify, measure, and improve the stability and accuracy of the design. An FEA (Finite Element Analysis) tool is used to determine the accuracy of the isolation transformer of the isolated analog acquisition system. The FEA tool assists in improving the isolation transformer's coupling accuracy by identifying the optimum placement of traces for the printed circuit board windings. The test results of a prototype circuit incorporated into an existing digital protective relay product are presented.

## TABLE OF CONTENTS

| Page                                                                            |

|---------------------------------------------------------------------------------|

| ACKNOWLEDGEMENTSiii                                                             |

| ABSTRACT iv                                                                     |

| LIST OF TABLESix                                                                |

| LIST OF FIGURESx                                                                |

| CHAPTER 1 INTRODUCTION1                                                         |

| 1.1 Background2                                                                 |

| 1.2 Thesis Scope and Content                                                    |

| 1.3 Isolated Analog Selector Circuit Overview                                   |

| 1.3.1 Concept                                                                   |

| 1.3.2 Design Challenges and Design Progression17                                |

| CHAPTER 2 ISOLATED ANALOG SELECTOR CIRCUIT DESIGN<br>HIGHLIGHTS                 |

| CHAPTER 3 ISOLATION TRANSFORMER CONSTRUCTION DETAILS                            |

| CHAPTER 4 ISOLATION TRANSFORMER MODELING                                        |

| 4.1 Typical B-H Characteristic of the Core Material                             |

| 4.2 Typical B-H Characteristic of the E-E Core                                  |

| 4.3 Printed Circuit Board Winding Resistance                                    |

| 4.4 Printed Circuit Board Winding Leakage Inductance and Winding<br>Capacitance |

| 4.5 SPICE Model of the Isolation Transformer                                    |

| CHAPTER 5 COMPENSATION OPERATIONAL AMPLIFIER CIRCUIT<br>PERFORMANCE             |

| 5.1 Control Loop Stability                                                      |

| 5.2                               | Stability and Settling Analysis of a 2 <sup>nd</sup> Order Passive Low Pass Filter<br>Using SPICE                                                                                                                                                                                                                                                                      | 59                                                          |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 5.3                               | Compensation Operational Amplifier SPICE Modeling, Stability and Accuracy                                                                                                                                                                                                                                                                                              | 65                                                          |

| 5.4                               | Lead/Lag Compensation With an Operational Amplifier                                                                                                                                                                                                                                                                                                                    | 76                                                          |

| 5.5                               | SPICE Modeling and Improving the Compensation Operational<br>Amplifier Circuitry                                                                                                                                                                                                                                                                                       | 83                                                          |

|                                   | 5.5.1 SPICE results of Compensation Operational Amplifier With Isolation Transformer                                                                                                                                                                                                                                                                                   | 83                                                          |

|                                   | 5.5.2 Driving the Magnetizing Inductance of the Isolation Transformer                                                                                                                                                                                                                                                                                                  | 85                                                          |

|                                   | 5.5.3 De-Q'ing the Isolation Transformer's Parasitics                                                                                                                                                                                                                                                                                                                  | 91                                                          |

|                                   | 5.5.4 Lead/ Lag Compensation                                                                                                                                                                                                                                                                                                                                           | 98                                                          |

| 5.6                               | Compensation Operational Amplifier Circuitry Stability and Accuracy                                                                                                                                                                                                                                                                                                    | 103                                                         |

| СНАРТ                             | TER 6 ISOLATION TRANSFORMER MAGNETIC COUPLING<br>ACCURACY                                                                                                                                                                                                                                                                                                              | 108                                                         |

|                                   |                                                                                                                                                                                                                                                                                                                                                                        |                                                             |

| 6.1                               | Transformer Modeling                                                                                                                                                                                                                                                                                                                                                   | 109                                                         |

| 6.1                               | Transformer Modeling      6.1.1 Self-Inductance                                                                                                                                                                                                                                                                                                                        |                                                             |

| 6.1                               |                                                                                                                                                                                                                                                                                                                                                                        | 111                                                         |

| 6.1                               | 6.1.1 Self-Inductance                                                                                                                                                                                                                                                                                                                                                  | 111<br>114                                                  |

| 6.1                               | <ul><li>6.1.1 Self-Inductance</li><li>6.1.2 Mutual Inductance</li></ul>                                                                                                                                                                                                                                                                                                | 111<br>114<br>116                                           |

|                                   | <ul> <li>6.1.1 Self-Inductance</li> <li>6.1.2 Mutual Inductance</li> <li>6.1.3 Two Winding Transformer Modeling</li> </ul>                                                                                                                                                                                                                                             | 111<br>114<br>116<br>125                                    |

| 6.2                               | <ul> <li>6.1.1 Self-Inductance</li> <li>6.1.2 Mutual Inductance</li> <li>6.1.3 Two Winding Transformer Modeling</li> <li>6.1.4 Three Winding Transformer Modeling</li> </ul>                                                                                                                                                                                           | 111<br>114<br>116<br>125<br>134                             |

| 6.2<br>6.3                        | <ul> <li>6.1.1 Self-Inductance</li> <li>6.1.2 Mutual Inductance</li> <li>6.1.3 Two Winding Transformer Modeling</li> <li>6.1.4 Three Winding Transformer Modeling</li> <li>Double 2-D Method</li> <li>Isolated Analog Selector Transformer Magnetic Coupling Accuracy</li> </ul>                                                                                       | 111<br>114<br>116<br>125<br>134<br>136                      |

| 6.2<br>6.3<br>CHAPT               | <ul> <li>6.1.1 Self-Inductance</li> <li>6.1.2 Mutual Inductance</li> <li>6.1.3 Two Winding Transformer Modeling</li> <li>6.1.4 Three Winding Transformer Modeling</li> <li>Double 2-D Method</li> <li>Isolated Analog Selector Transformer Magnetic Coupling Accuracy Analysis</li> </ul>                                                                              | 111<br>114<br>116<br>125<br>134<br>136<br>142               |

| 6.2<br>6.3<br>CHAPT<br>7.1        | <ul> <li>6.1.1 Self-Inductance</li> <li>6.1.2 Mutual Inductance</li> <li>6.1.3 Two Winding Transformer Modeling</li> <li>6.1.4 Three Winding Transformer Modeling</li> <li>Double 2-D Method</li> <li>Isolated Analog Selector Transformer Magnetic Coupling Accuracy<br/>Analysis</li> <li>TER 7 PROTOTYPE TESTING AND RESULTS</li> </ul>                             | 111<br>114<br>116<br>125<br>134<br>136<br>142<br>142        |

| 6.2<br>6.3<br>CHAPT<br>7.1<br>7.2 | <ul> <li>6.1.1 Self-Inductance</li> <li>6.1.2 Mutual Inductance</li> <li>6.1.3 Two Winding Transformer Modeling</li> <li>6.1.4 Three Winding Transformer Modeling</li> <li>Double 2-D Method</li> <li>Isolated Analog Selector Transformer Magnetic Coupling Accuracy<br/>Analysis</li> <li>TER 7 PROTOTYPE TESTING AND RESULTS</li> <li>Prototype Overview</li> </ul> | 111<br>114<br>116<br>125<br>134<br>136<br>142<br>142<br>142 |

| 7.5 Channel to Channel Crosstalk Performance  | 156 |

|-----------------------------------------------|-----|

| CHAPTER 8 CONCLUSIONS                         | 161 |

| APPENDIX A SPICE MODELS                       |     |

| A.1 E-E Core Models                           |     |

| A.2 OPA357 Model (Courtesy Texas Instruments) | 164 |

| BIBLIOGRAPHY                                  |     |

## LIST OF TABLES

| Table 4-1: | Jiles-Atherton Parameters for the nine versions of E-E core SPICE<br>models representing the part-to-part variations as well as the<br>temperature extreme variations | 47  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 4-2: | Variation in winding resistance due to printed circuit board variances<br>and temperature extremes                                                                    | 51  |

| Table 4-3: | Leakage inductance of the printed circuit board drive, sense, and signal printed circuit board windings                                                               | 52  |

| Table 4-4: | Capacitances associated with the printed circuit board windings                                                                                                       | 53  |

| Table 5-1: | Open loop gain versus error (%)                                                                                                                                       | 71  |

| Table 6-1: | Inductances and magnetic coupling error for interleaved drive and sense windings.                                                                                     | 139 |

| Table 6-2: | Magnetic coupling error for various locations of the sense winding                                                                                                    | 141 |

| Table 7-1: | Type test performed on SEL-421 with Isolated Analog Selector prototype VT and CT channels.                                                                            | 155 |

| Table 7-2: | Type test margin results for the Isolated Analog Selector and SEL-421 traditional VT and CT channels.                                                                 | 156 |

## LIST OF FIGURES

| Figure 1-1: | Block diagram of a traditional acquisition system for a digital protective relay with six VT and six CT channels.                                                                                                                                                                      | 10 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1-2: | Voltage signal at the A-D converter, with a 60 Hz ac voltage signal<br>on Channel 1 and the signals from the other channels blanked out                                                                                                                                                | 12 |

| Figure 1-3: | Concept block diagram of a new transformer isolated data acquisition system.                                                                                                                                                                                                           | 14 |

| Figure 1-4: | Approximated spectral content of the transformer on/off switching action convolved with the spectral content of a typical LPF output voltage signal, $V_{LPF}$ (normalized to the rms fundamental of $V_{LPF}$ )                                                                       | 16 |

| Figure 1-5: | First approximation circuit model for the isolation transformer                                                                                                                                                                                                                        | 17 |

| Figure 1-6: | Isolated Analog Selector circuit concept block diagram                                                                                                                                                                                                                                 | 19 |

| Figure 2-1: | Isolated Analog Selector circuit block diagram.                                                                                                                                                                                                                                        | 23 |

| Figure 2-2: | Isolated Analog Selector Channel 1 Timing Diagram.                                                                                                                                                                                                                                     | 25 |

| Figure 2-3: | Trigger signal timing diagram                                                                                                                                                                                                                                                          | 26 |

| Figure 3-1: | Isolation transformer schematic.                                                                                                                                                                                                                                                       | 30 |

| Figure 3-2: | Isolation transformer construction using an E-E ferrite core and<br>printed circuit board traces for windings: (a) expanded component<br>view, (b) assembled view [primary and secondary printed circuit<br>boards overlap where the E-E core is located] (c) cross sectional<br>view. | 31 |

| Figure 3-3: | Signal winding, 11 turns on one of the inner printed circuit board layers.                                                                                                                                                                                                             | 32 |

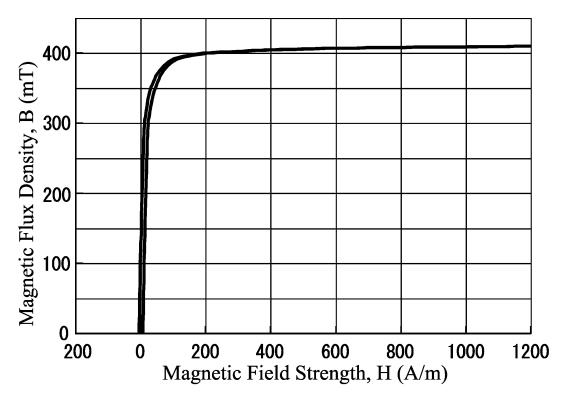

| Figure 4-1: | Tomita 2G1 material B-H characteristic.                                                                                                                                                                                                                                                | 35 |

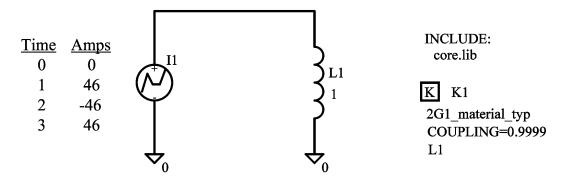

| Figure 4-2: | SPICE model schematic for plotting the B-H characteristic                                                                                                                                                                                                                              | 37 |

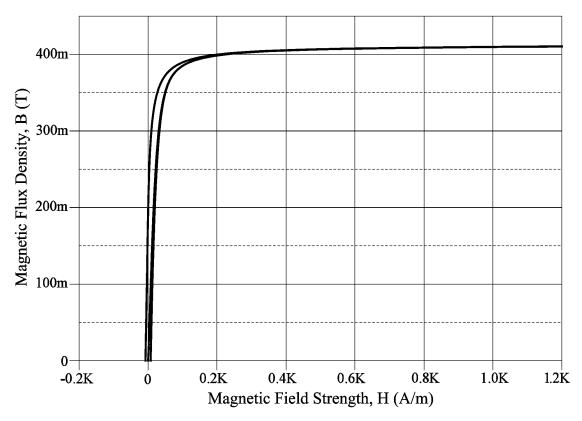

| Figure 4-3: | Material B-H characteristic plot from SPICE.                                                                                                                                                                                                                                           | 37 |

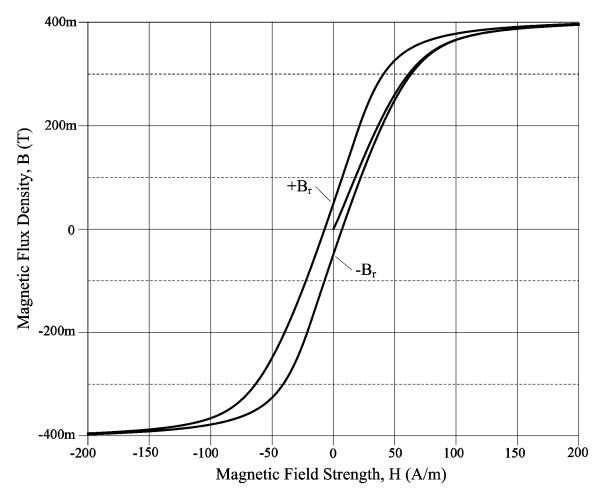

| Figure 4-4: | E-E core B-H characteristic plot from SPICE                                                                                                                                                                                                                                            | 39 |

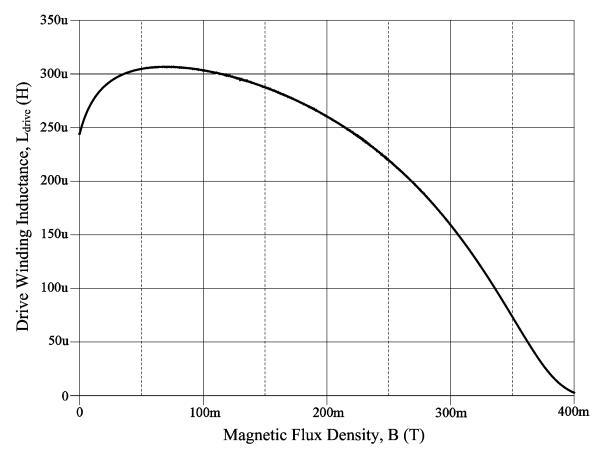

| Figure 4-5: | Inductance for the $N = 9$ turn drive winding as a function of magnetic flux density for the B-H characteristic path from $B = H = 0$ to saturation.                                                                                                                                   | 42 |

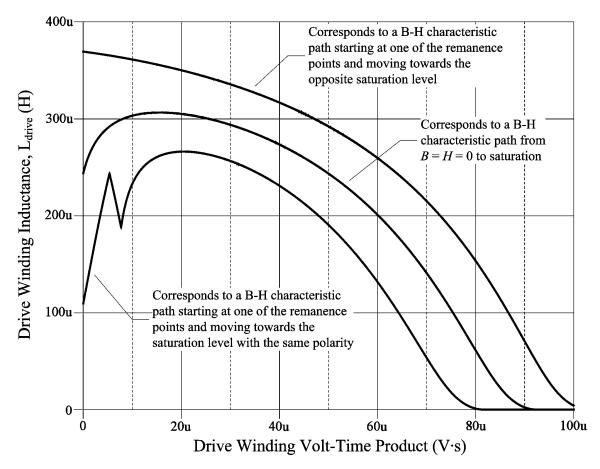

| Figure 4-6: | Inductance for the $N = 9$ turn drive winding as a function of the applied volt-time product.                                                                     | 44 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

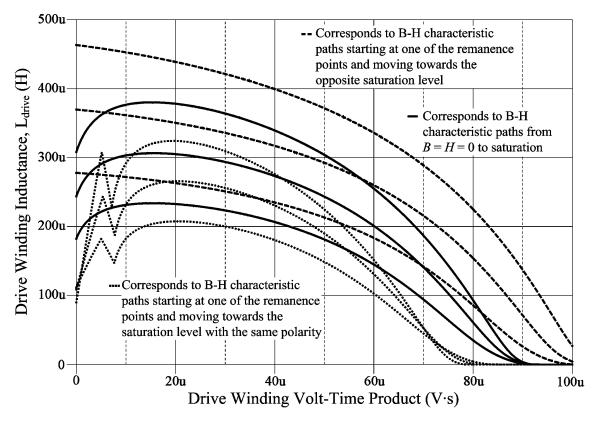

| Figure 4-7: | Minimum, typical and maximum inductance (at room temperature) for the $N = 9$ turn drive winding as a function of the applied volt-time product                   | 46 |

| Figure 4-8: | B-H characteristics for the typical E-E core SPICE models for 25 °C, 100 °C and –40 °C                                                                            | 48 |

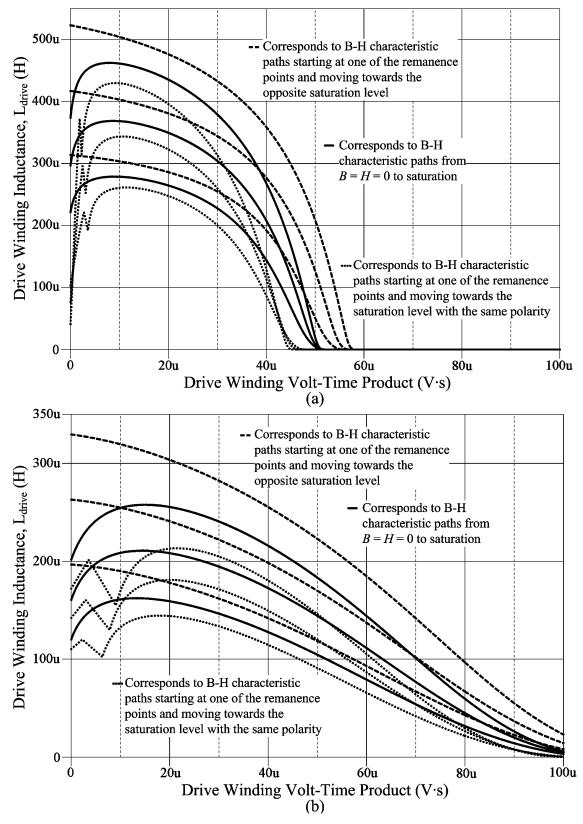

| Figure 4-9: | Minimum, typical and maximum inductance for the $N = 9$ turn drive<br>winding as a function of the applied volt-time product: (a) at 100 °C<br>and (b) at -40 °C. | 49 |

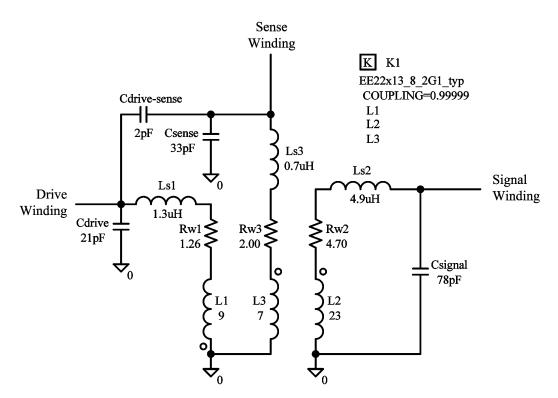

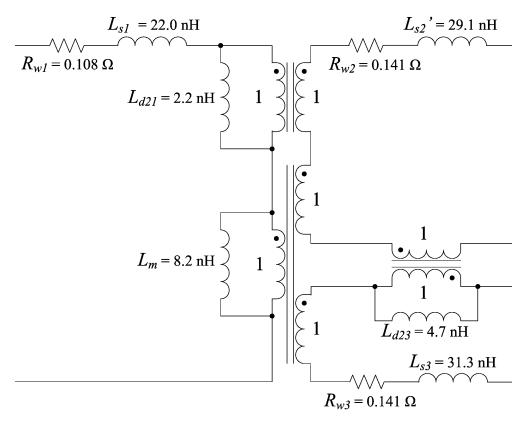

| Figure 4-10 | : SPICE model of the Isolation Transformer                                                                                                                        | 54 |

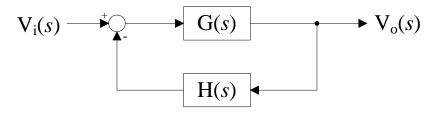

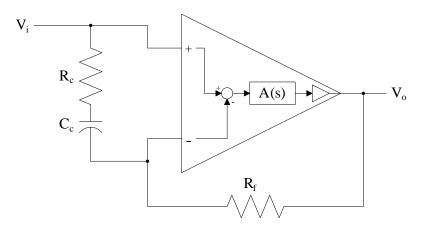

| Figure 5-1: | Basic control loop                                                                                                                                                | 57 |

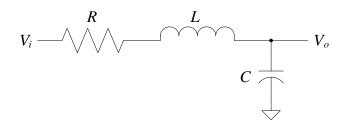

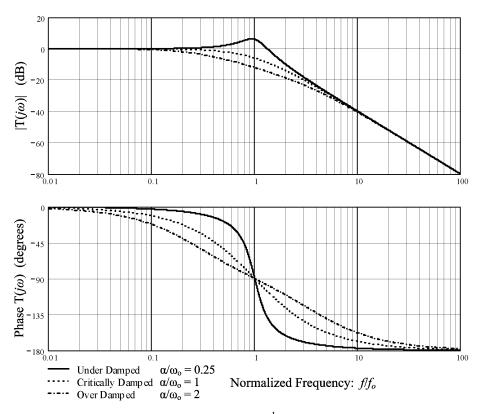

| Figure 5-2: | 2 <sup>nd</sup> order passive low pass filter.                                                                                                                    | 59 |

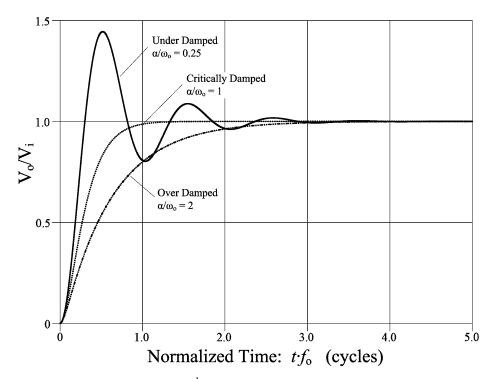

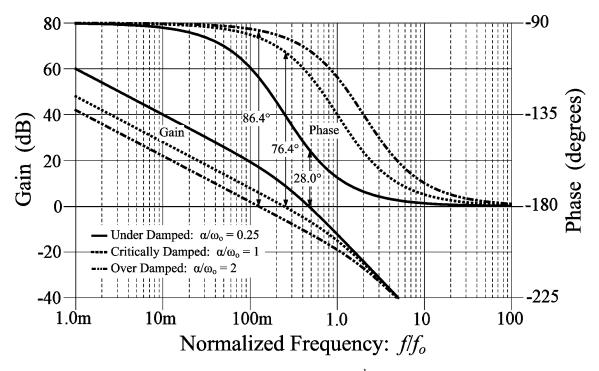

| Figure 5-3: | Transfer function Bode plots for 2 <sup>nd</sup> order low pass system (under damped, critically damped, and over damped).                                        | 60 |

| Figure 5-4: | Step response for 2 <sup>nd</sup> order low pass system (under damped, critically damped, and over damped).                                                       | 60 |

| Figure 5-5: | Control loop for 2 <sup>nd</sup> order low pass system                                                                                                            | 61 |

| Figure 5-6: | Open loop gain/phase plot for 2 <sup>nd</sup> order low pass system                                                                                               | 62 |

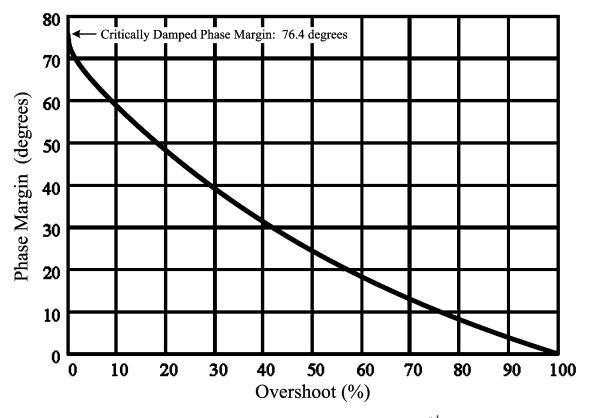

| Figure 5-7: | % Overshoot versus phase margin for 2 <sup>nd</sup> order system.                                                                                                 | 63 |

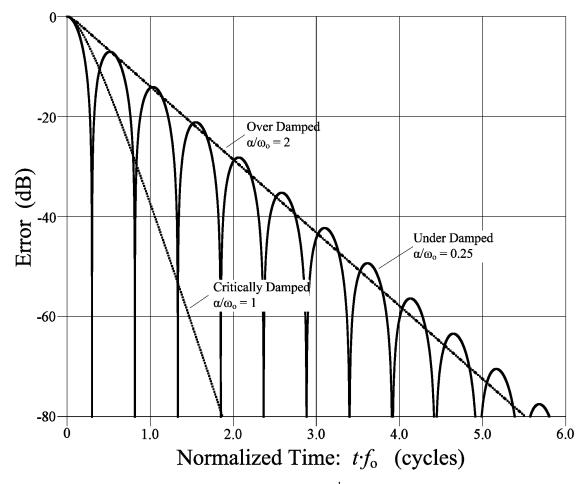

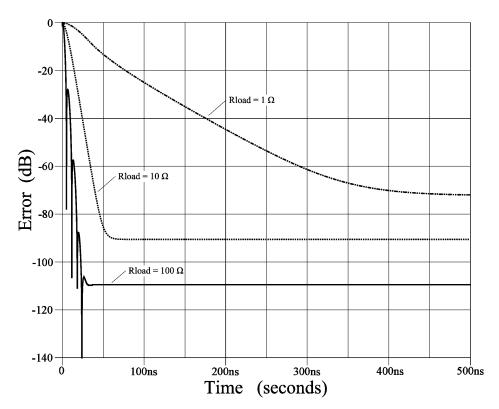

| Figure 5-8: | Settling time/error for 2 <sup>nd</sup> order low pass system                                                                                                     | 64 |

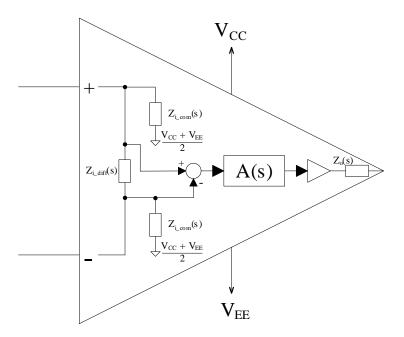

| Figure 5-9: | Operational amplifier transfer function elements                                                                                                                  | 65 |

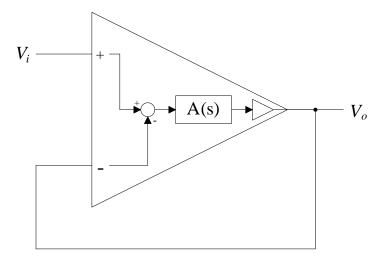

| Figure 5-10 | : Operational amplifier voltage follower                                                                                                                          | 66 |

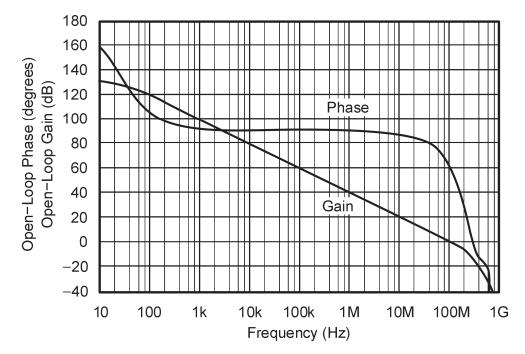

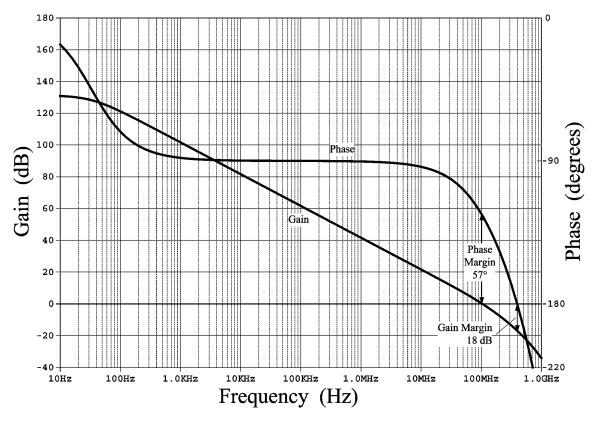

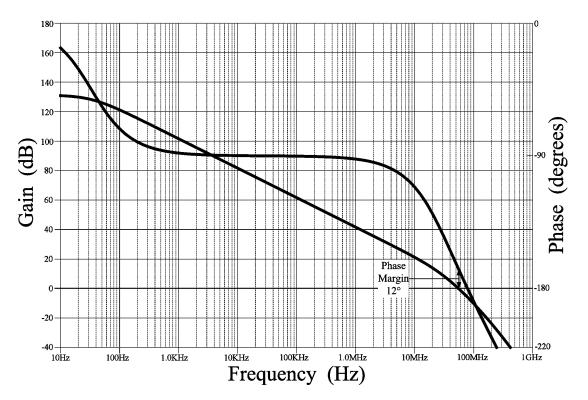

| Figure 5-11 | : OPA357 datasheet open loop gain/phase plot (Courtesy Texas Instruments)                                                                                         | 66 |

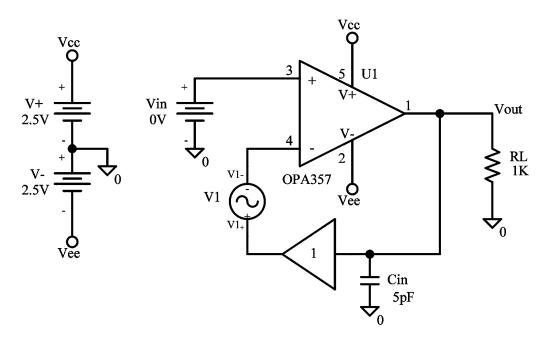

| Figure 5-12 | : SPICE schematic for generating OPA357 open loop gain and phase plot                                                                                             | 68 |

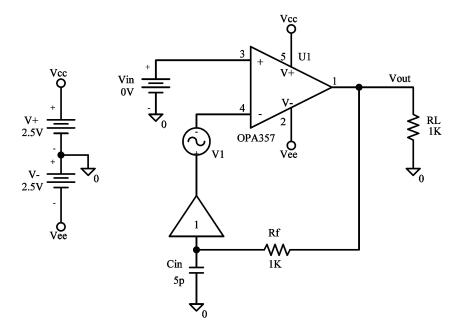

| Figure 5-13 | : OPA357 open loop gain/phase plot using SPICE.                                                                                                                   | 69 |

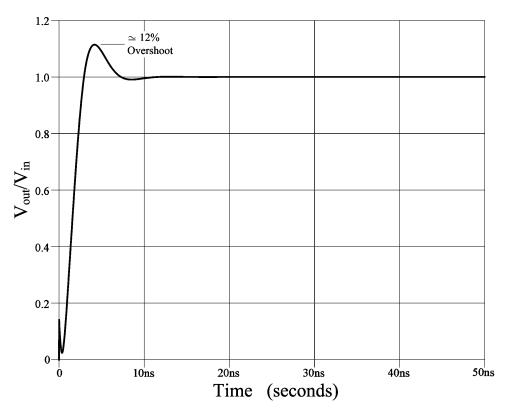

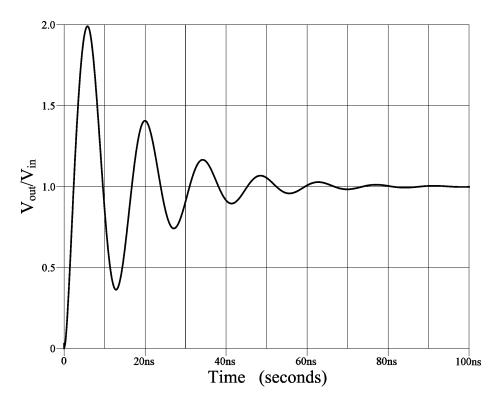

| Figure 5-14 | : Step response for OPA357 voltage follower using SPICE.                                                                                                          | 70 |

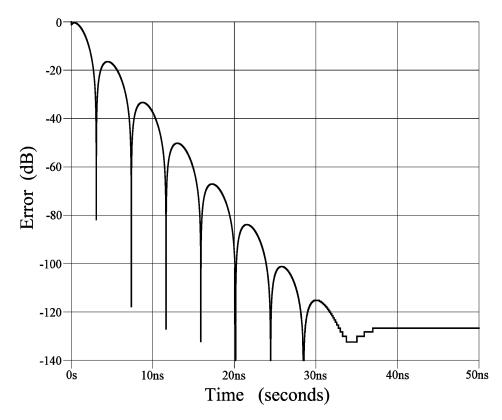

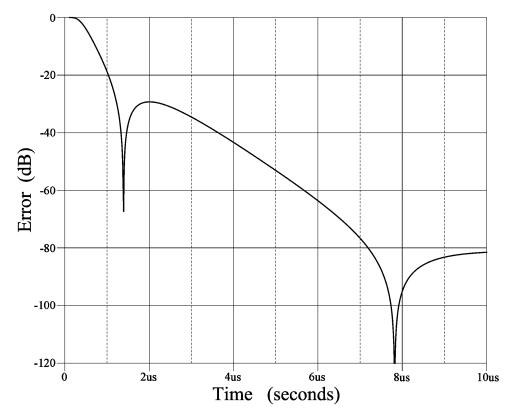

| Figure 5-15 | : Settling time error for OPA357 voltage follower using SPICE                                                                                                     | 70 |

| Figure 5-16: | OPA357 datasheet open loop gain and phase plot (Courtesy Texas<br>Instruments)                                | .72  |

|--------------|---------------------------------------------------------------------------------------------------------------|------|

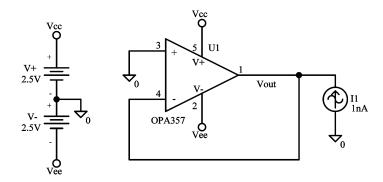

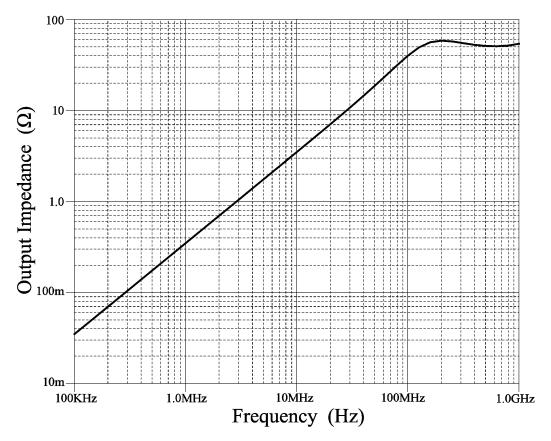

| Figure 5-17: | SPICE model schematic for generating OPA357 closed loop output impedance plot.                                | .73  |

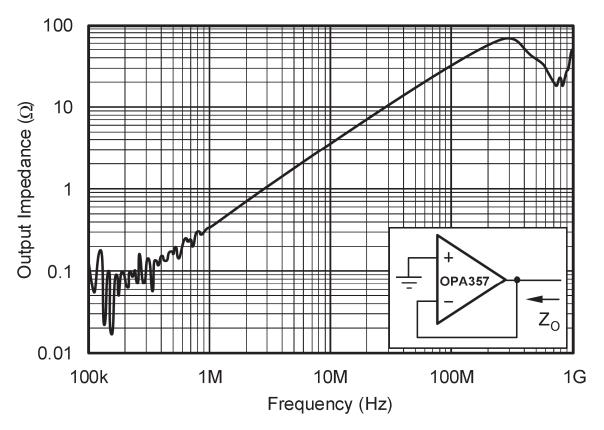

| Figure 5-18: | OPA357 closed loop output impedance plot using SPICE.                                                         | .73  |

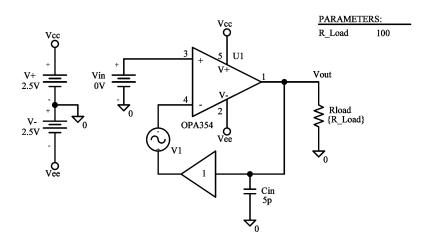

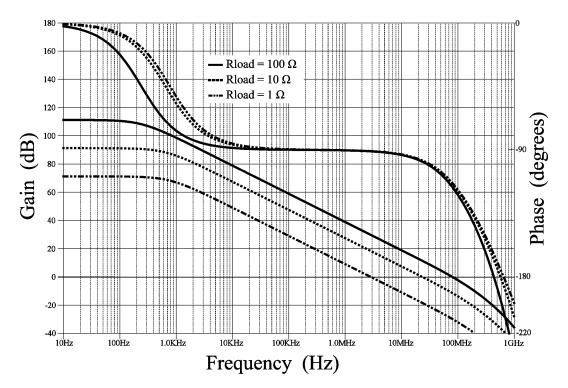

| Figure 5-19: | SPICE model schematic for generating gain/phase plot of OPA357 voltage follower with resistive output loading | .74  |

| Figure 5-20: | OPA357 voltage follower with resistive output loading open loop gain/phase plot using SPICE.                  | .75  |

| Figure 5-21: | OPA357 voltage follower with resistive output loading settling time error using SPICE.                        | .75  |

| Figure 5-22: | SPICE model schematic for generating gain/phase plot of OPA357 voltage follower with feedback resistance.     | .76  |

| Figure 5-23: | OPA357 voltage follower with feedback resistance open loop gain/phase plot using SPICE.                       | .77  |

| Figure 5-24: | Step response for OPA357 voltage follower with feedback resistance using SPICE.                               | .77  |

| Figure 5-25: | Classic operational amplifier lead/lag compensation                                                           | .78  |

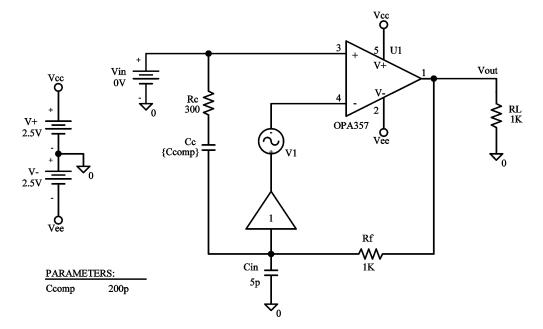

| Figure 5-26: | SPICE model schematic for OPA357 voltage follower with lead/lag compensation.                                 | .79  |

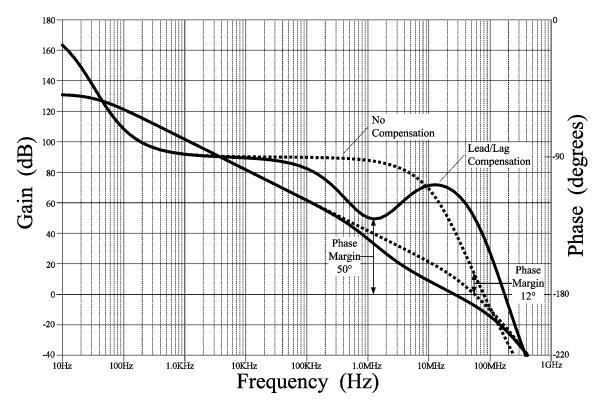

| Figure 5-27: | OPA357 voltage follower with lead/lag compensation open loop gain/phase plot using SPICE.                     | . 80 |

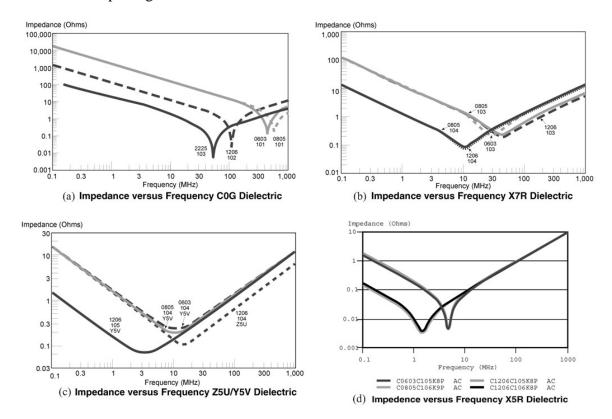

| Figure 5-28: | SMT (Surface Mount Technology) capacitor frequency response                                                   | . 81 |

| Figure 5-29: | Step response for OPA357 voltage follower with lead/lag compensation using SPICE.                             | . 82 |

| Figure 5-30: | OPA357 voltage follower with lead/lag compensation settling time error using SPICE.                           | . 82 |

| Figure 5-31: | SPICE model schematic for OPA357 compensation operational amplifier with isolation transformer                | . 84 |

| Figure 5-32: | OPA357 compensation operational amplifier with isolation transformer open loop gain/phase plot using SPICE.   | . 85 |

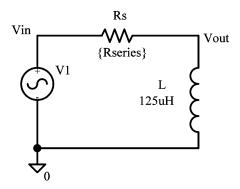

| Figure 5-33: | SPICE model schematic for resistor/inductor high pass filter.                                                 | . 86 |

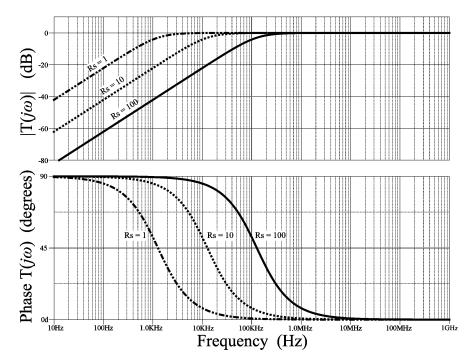

| Figure 5-34: | Transfer function Bode plots for resistor/inductor high pass filter                                                                                                   | 87    |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

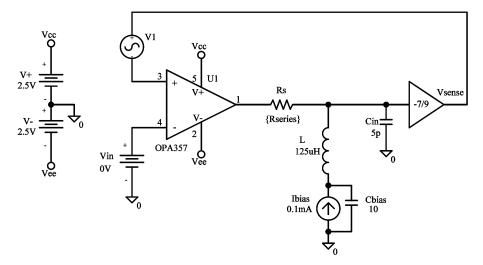

| Figure 5-35: | SPICE model schematic for OPA357 driving the magnetizing inductance of the isolation transformer.                                                                     | 87    |

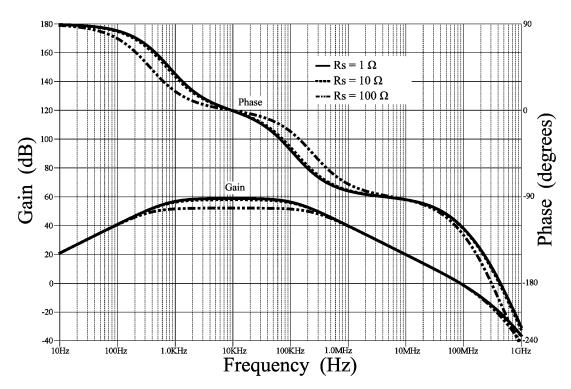

| Figure 5-36: | OPA357 driving the magnetizing inductance of the isolation transformer, open loop gain/phase plot using SPICE.                                                        | 89    |

| Figure 5-37: | OPA357 driving the magnetizing inductance of the isolation transformer, settling time error using SPICE.                                                              | 89    |

| Figure 5-38: | SPICE model schematic for OPA357 with class B push-pull drive amplifier stage.                                                                                        | 90    |

| Figure 5-39: | OPA357 with class B push-pull drive amplifier stage, open loop gain/phase plot using SPICE.                                                                           | 91    |

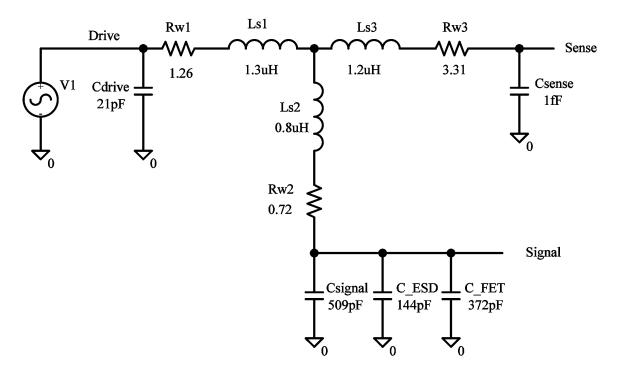

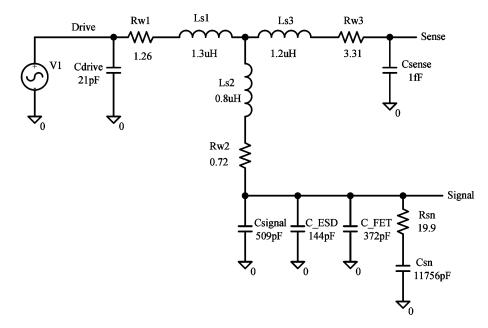

| Figure 5-40: | SPICE model schematic for the typical parasitics of isolation transformer circuit.                                                                                    | 92    |

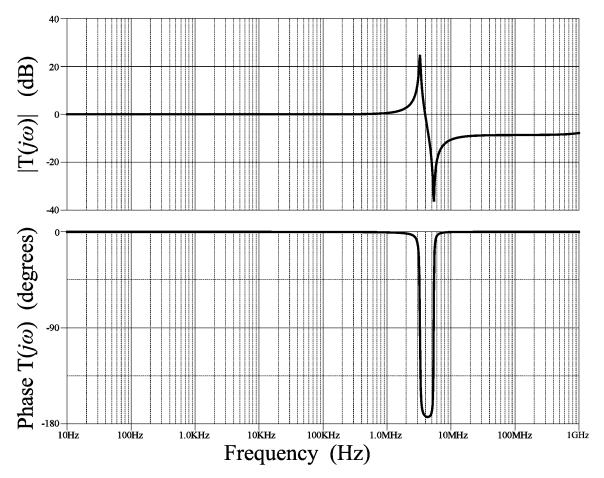

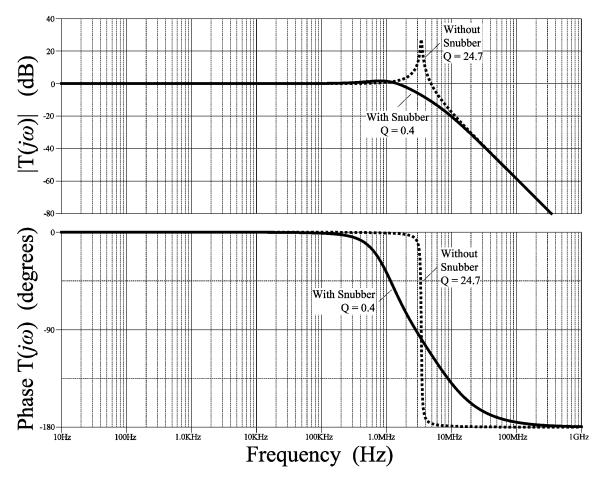

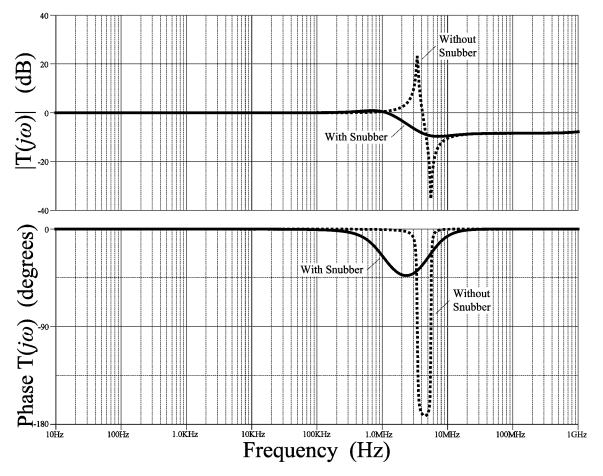

| Figure 5-41: | Drive to sense winding transfer function Bode plots for the typical parasitics of isolation transformer circuit                                                       | 93    |

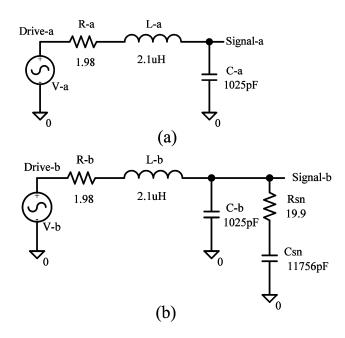

| Figure 5-42: | SPICE model schematic for: (a) transfer function between drive and signal nodes, and (b) transfer function between drive and signal nodes with additional R-C snubber | 94    |

| Figure 5-43: | Transfer function Bode plots for additional R-C snubber                                                                                                               | 95    |

| Figure 5-44: | SPICE model schematic for the typical parasitics of isolation transformer circuit with additional R-C snubber                                                         | 95    |

| Figure 5-45: | Transfer function Bode plots for typical parasitic of isolation transformer circuit with additional snubber.                                                          | 96    |

| Figure 5-46: | SPICE model schematic for OPA357 circuit with R-C snubber/output filter.                                                                                              | 97    |

| Figure 5-47: | OPA357 circuit with snubber/output filter, open loop gain/phase plot using SPICE.                                                                                     | 98    |

| Figure 5-48: | SPICE model schematic for OPA357 circuit with lead/lag compensation.                                                                                                  | 99    |

| Figure 5-49: | OPA357 circuit with lead/lag compensation, open loop gain/phase plot using SPICE.                                                                                     | 99    |

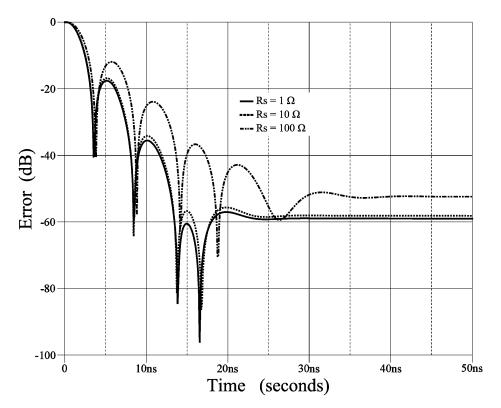

| Figure 5-50: | OPA357 circuit with lead/lag compensation, settling time error using SPICE.                                                                                           | . 100 |

| Figure 5-51:  | SPICE model schematic for OPA357 circuit with improved lead/lag compensation                                                                                                                                                                                                                    | 101 |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5-52:  | OPA357 circuit with improved lead/lag compensation, open loop gain/phase plot using SPICE.                                                                                                                                                                                                      | 102 |

| Figure 5-53:  | OPA357 circuit with improved lead/lag compensation, settling time error using SPICE.                                                                                                                                                                                                            | 103 |

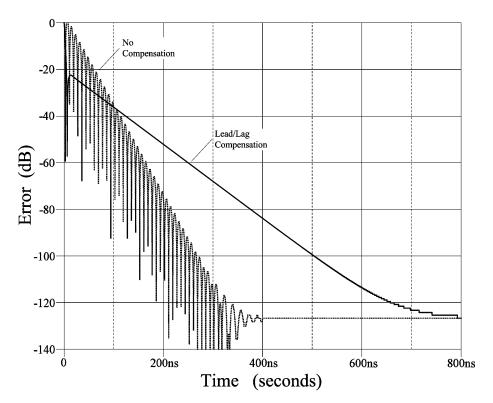

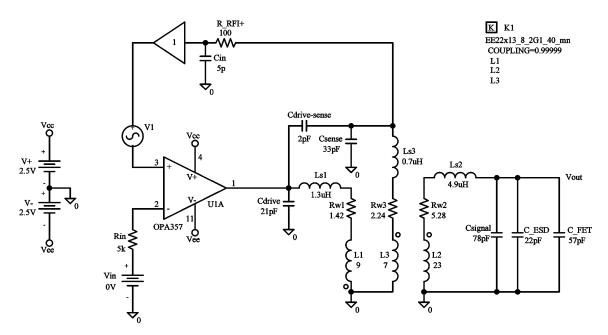

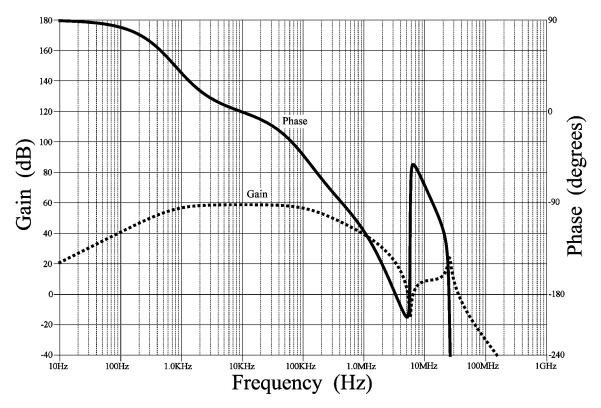

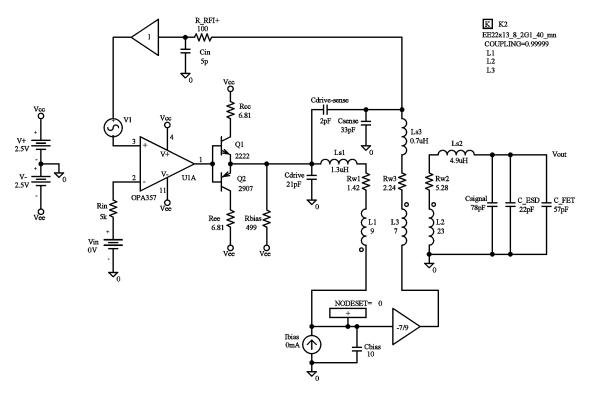

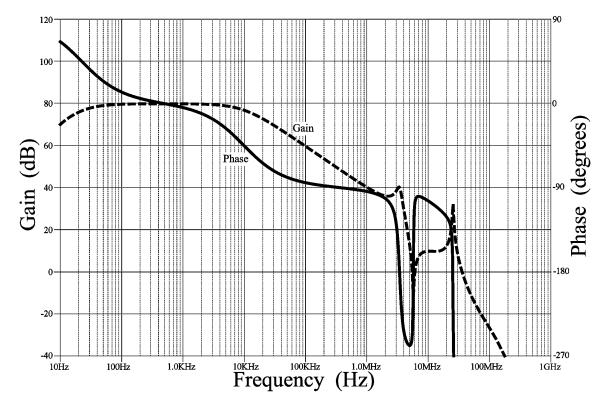

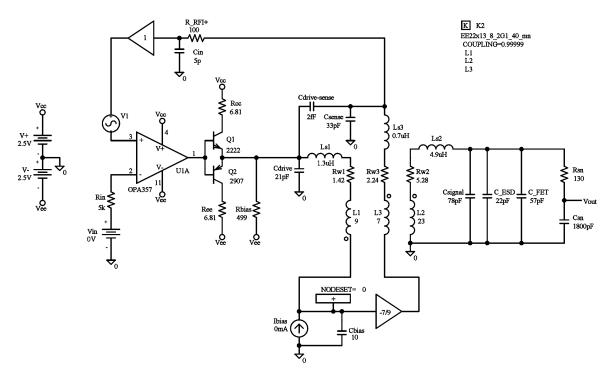

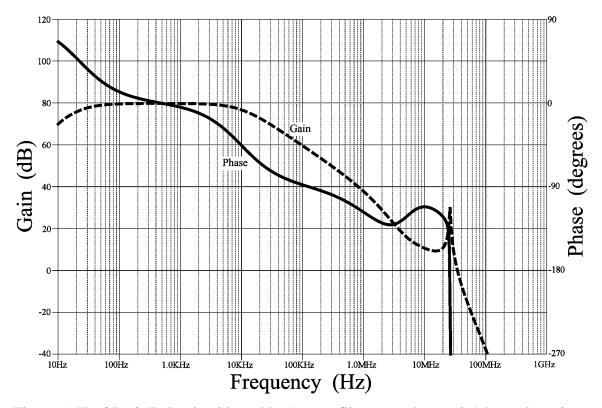

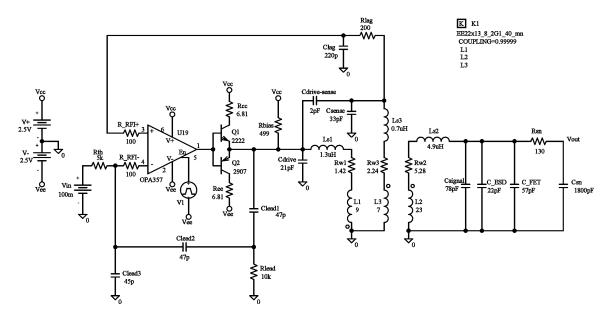

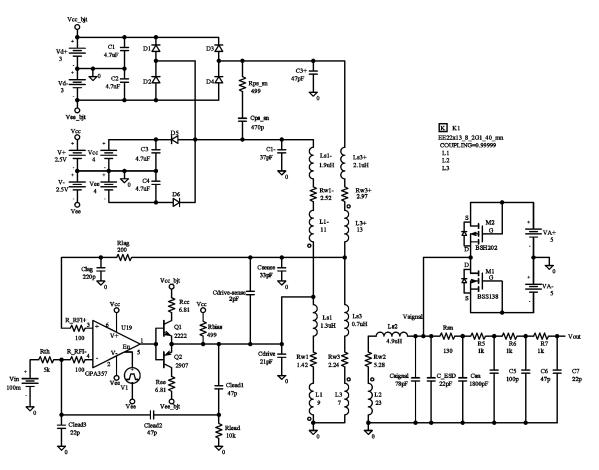

| Figure 5-54:  | SPICE model schematic for compensation operational amplifier circuitry.                                                                                                                                                                                                                         | 104 |

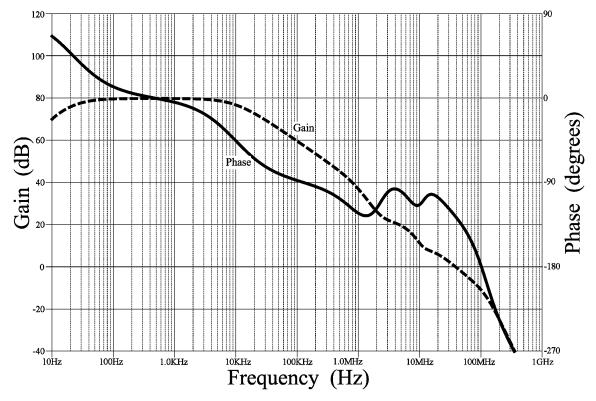

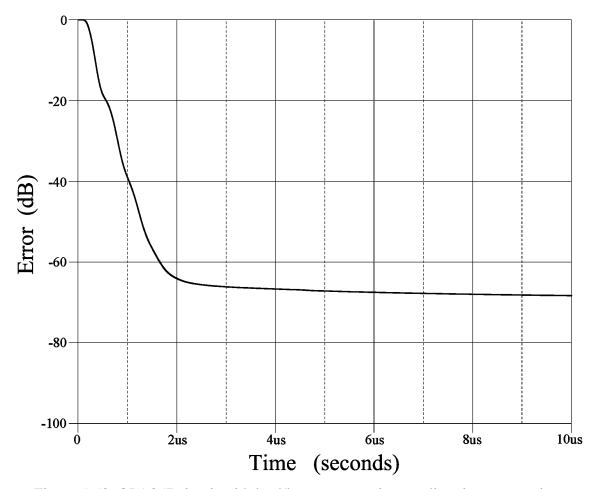

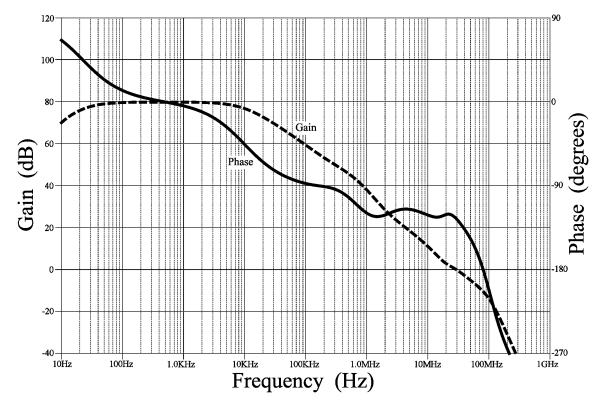

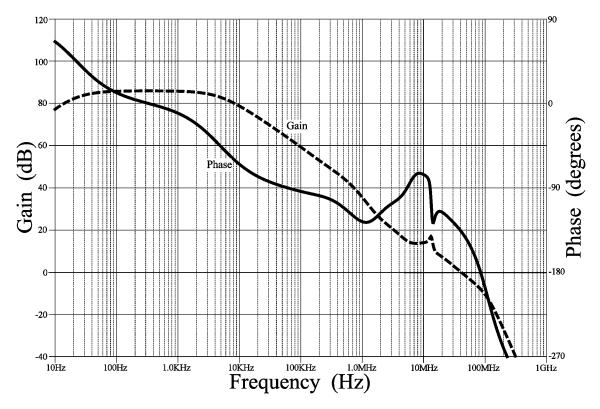

| Figure 5-55:  | Compensation operational amplifier circuitry, open loop gain/phase plot using SPICE.                                                                                                                                                                                                            | 105 |

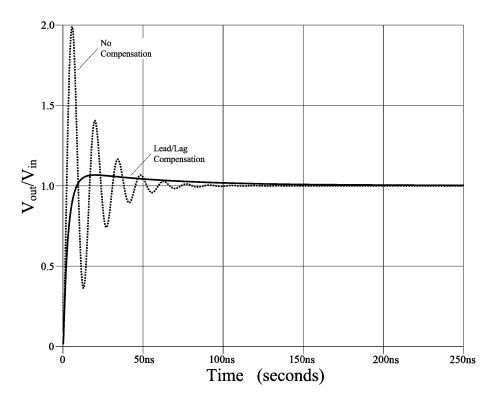

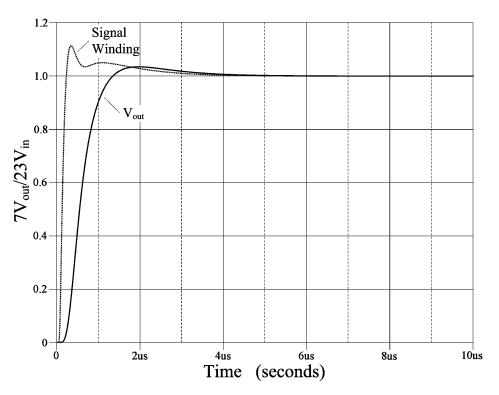

| Figure 5-56:  | Step response for compensation operational amplifier circuitry using SPICE.                                                                                                                                                                                                                     | 106 |

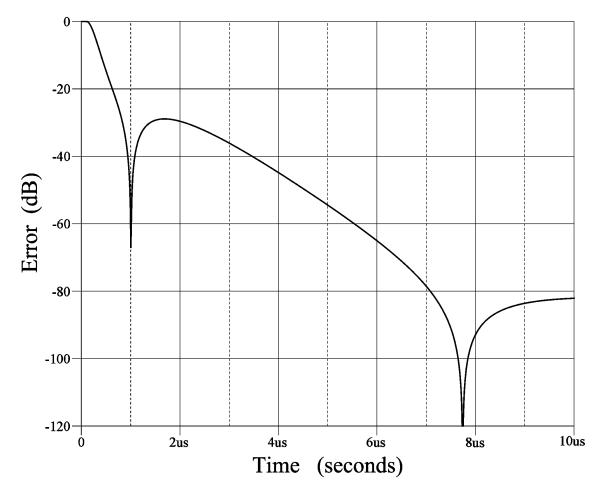

| Figure 5-57:  | Compensation operational amplifier circuitry, settling time error using SPICE.                                                                                                                                                                                                                  | 106 |

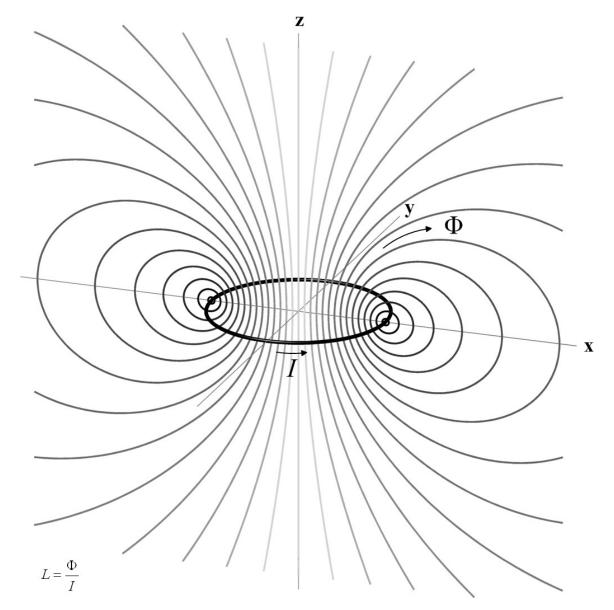

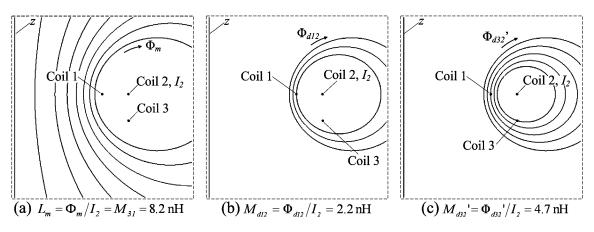

| Figure 6-1: N | Magnetic flux, $\Phi$ , produced by a single coil of wire being driven by current, <i>I</i> .                                                                                                                                                                                                   | 113 |

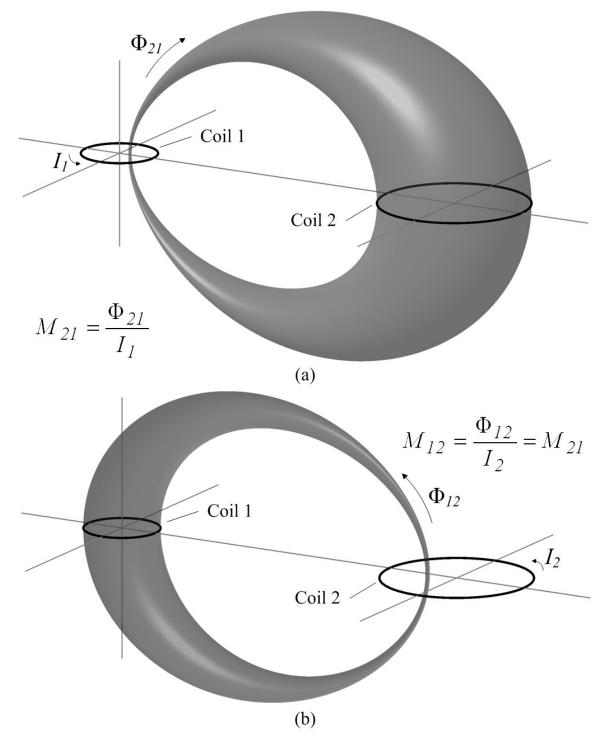

| Figure 6-2: I | Mutual inductance and corresponding magnetic flux: (a) Magnetic flux, $\Phi_{21}$ , coupling to Coil 2 due to $I_1$ flowing only in Coil 1, (b) Magnetic flux, $\Phi_{12}$ , coupling to Coil 1 due to $I_2$ flowing only in Coil 2.                                                            | 115 |

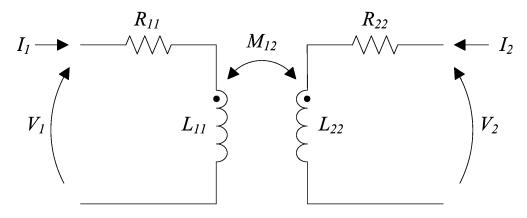

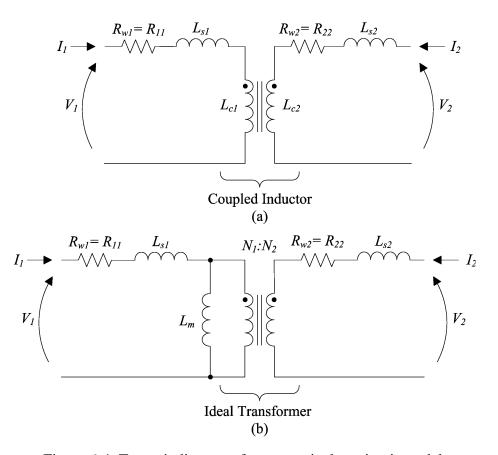

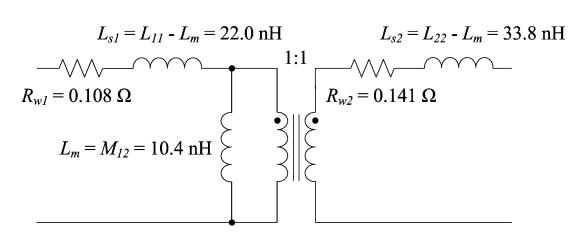

| Figure 6-3: 1 | Гwo winding transformer circuit model                                                                                                                                                                                                                                                           |     |

| Figure 6-4: 7 | Two winding transformer equivalent circuit model                                                                                                                                                                                                                                                | 117 |

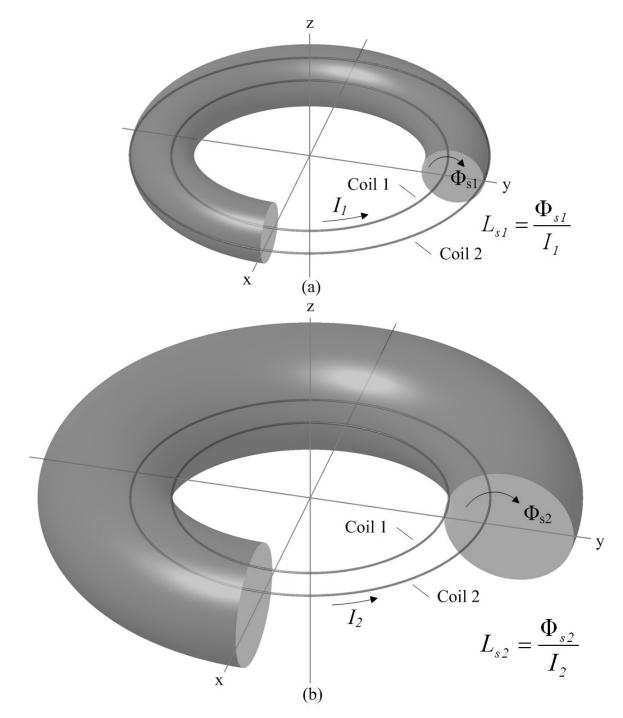

| Figure 6-5: I | Leakage inductance and corresponding magnetic flux in free space:<br>(a) Leakage flux, $\Phi_{s1}$ , coupling to Coil 1 (but not to Coil 2) due to $I_1$ flowing only in Coil 1, (b) Magnetic flux, $\Phi_{s2}$ , coupling to Coil 2<br>(but not to Coil 1) due to $I_2$ flowing only in Coil 2 | 120 |

| Figure 6-6: 1 | Fransformer equivalent circuit model for two single turn coils                                                                                                                                                                                                                                  | 122 |

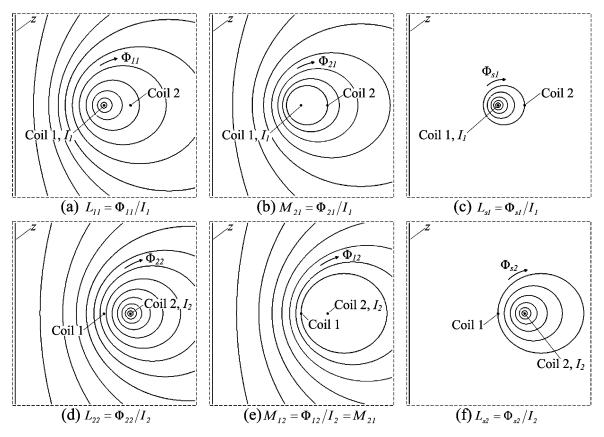

| Figure 6-7: N | Magnetic flux and corresponding inductances associated with two single turn coils.                                                                                                                                                                                                              | 123 |

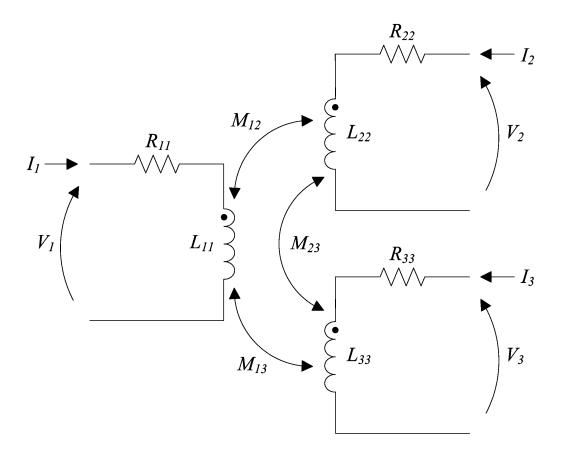

| Figure 6-8: 1 | Three winding transformer circuit model                                                                                                                                                                                                                                                         | 125 |

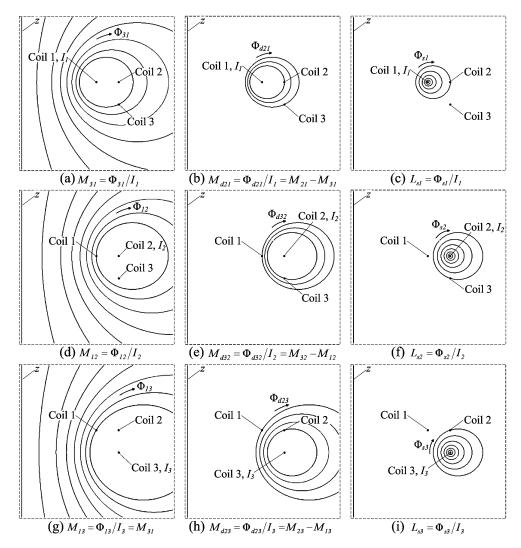

| Figure 6-9: N | Magnetic flux and corresponding inductances associated with three single turn coils.                                                                                                                                                                                                            | 127 |

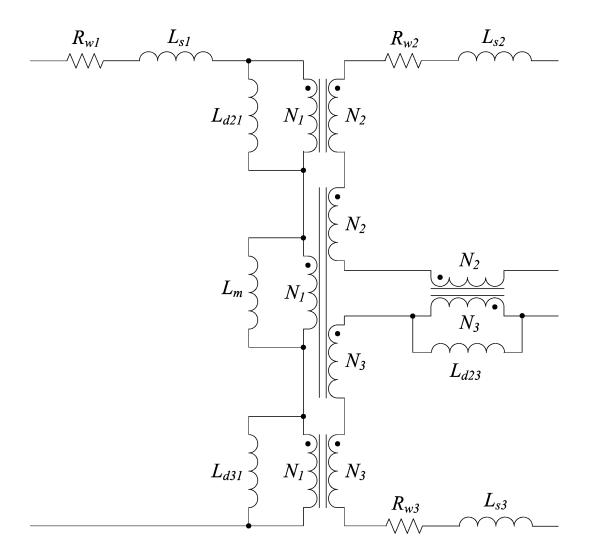

| Figure 6-10:  | Three winding transformer equivalent circuit model                                                                                                                                                                                               | . 129 |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 6-11:  | Transformer equivalent circuit model for three single turn coils                                                                                                                                                                                 | .131  |

| Figure 6-12:  | : Magnetic flux associated with driving Coil 2 with <i>I</i> <sub>2</sub>                                                                                                                                                                        | .132  |

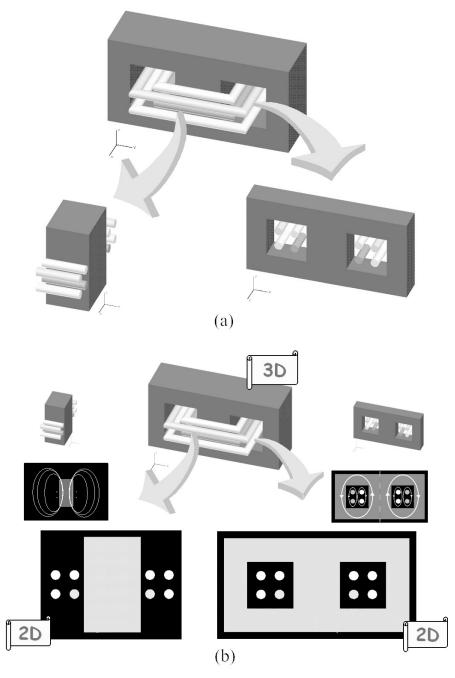

| Figure 6-13:  | Double 2-D method: (a) division of windings and core into two orthogonal segment sets; (b) frontal and lateral 2-D solutions.                                                                                                                    | .135  |

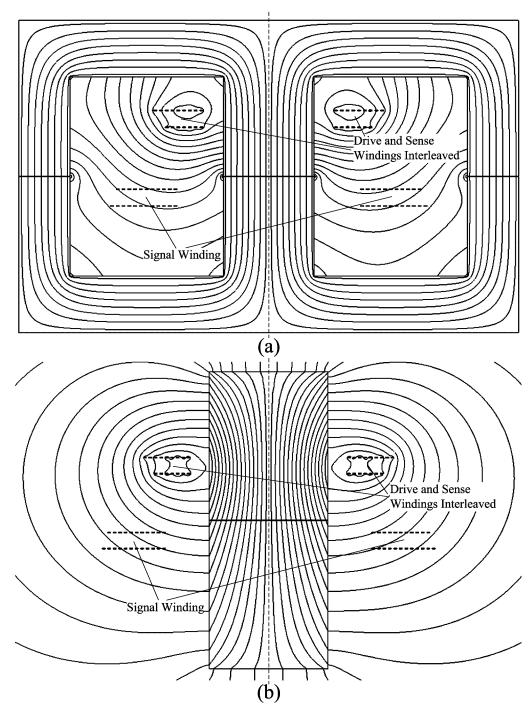

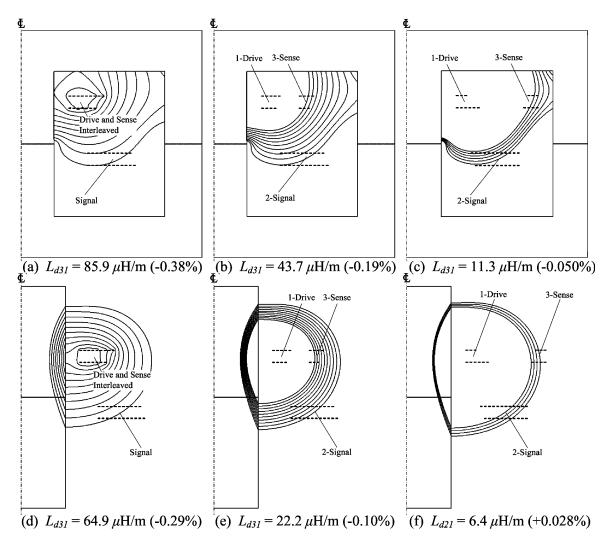

| Figure 6-14:  | Double 2-D solution for Isolated Analog Selector transformer with interleaved drive and sense windings: (a) frontal solution; (b) lateral solution.                                                                                              | .137  |

| Figure 6-15:  | Magnetic flux and corresponding inductance associated with drive winding: (a), (b), (c) frontal solution; (d), (e), (f) lateral solution                                                                                                         | .138  |

| Figure 6-16:  | Magnetic flux associated with drive winding: (a), & (d) drive and<br>sense windings interleaved; (b) & (e) sense winding near middle of<br>printed circuit board; (c) & (f) sense winding near outer edge of<br>printed circuit board (optimal). | . 140 |

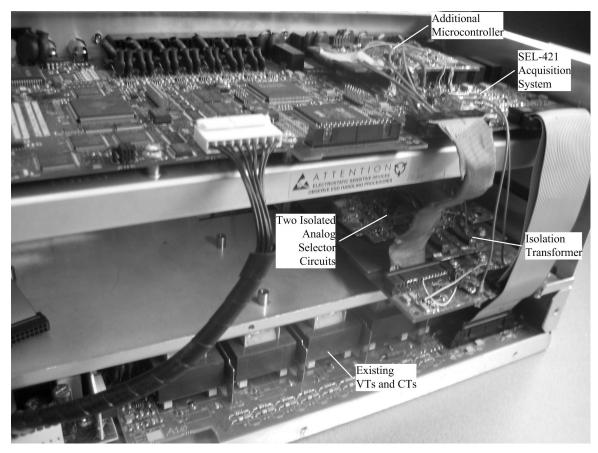

| Figure 7-1:   | Two Isolated Analog Selector prototype circuits added to the SEL-421<br>(replacement of one VT and one CT)                                                                                                                                       | . 143 |

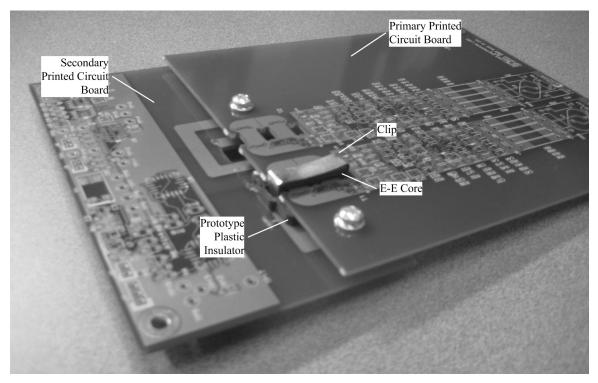

| Figure 7-2: ] | Isolation transformer conceptual prototype                                                                                                                                                                                                       | .144  |

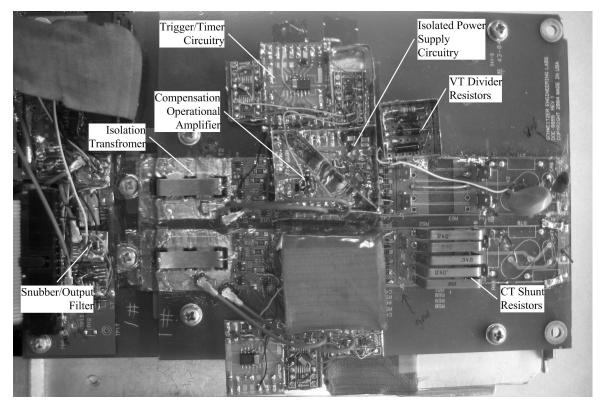

| Figure 7-3:   | Isolated Analog Selector prototype circuitry                                                                                                                                                                                                     | . 145 |

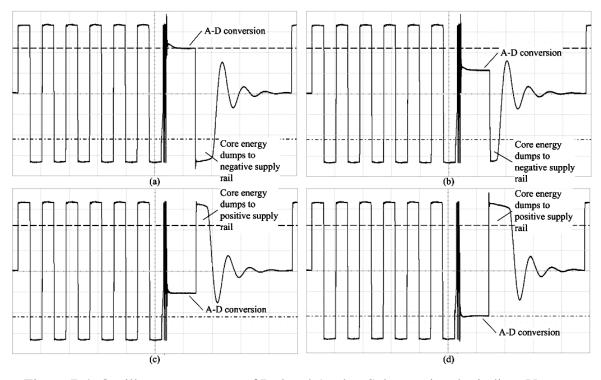

| Figure 7-4: 0 | Oscilloscope captures of Isolated Analog Selector signal winding,<br>$V_{LPF}$ = : (a) + full scale; (b) + <sup>1</sup> / <sub>2</sub> full scale; (c) - <sup>1</sup> / <sub>2</sub> full scale; (d) - full<br>scale.                            | .146  |

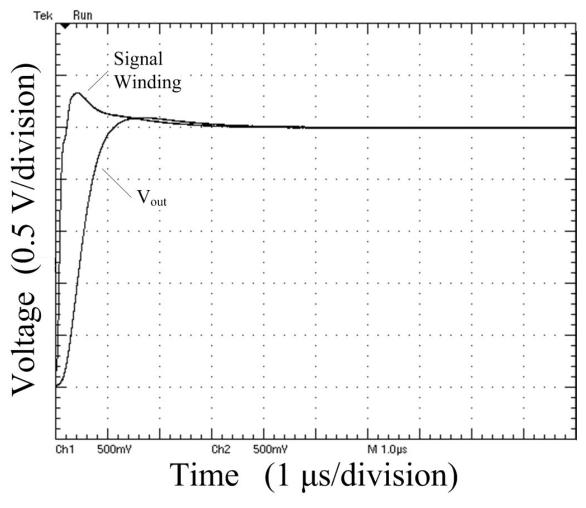

| Figure 7-5:   | Oscilloscope capture: step response of signal winding and Isolated<br>Analog Selector output voltage, V <sub>out</sub> (2.5 V step, 10 µs)                                                                                                       | . 147 |

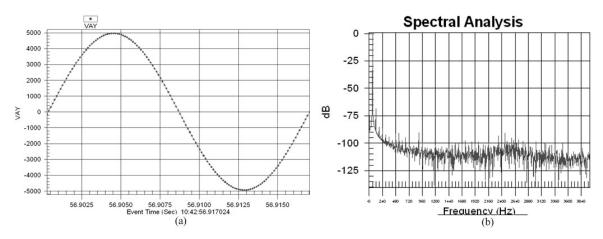

| Figure 7-6: S | Sampled data from SEL-421 with 350 V <sub>rms</sub> applied to VAY (Isolated Analog Selector channel).                                                                                                                                           | . 148 |

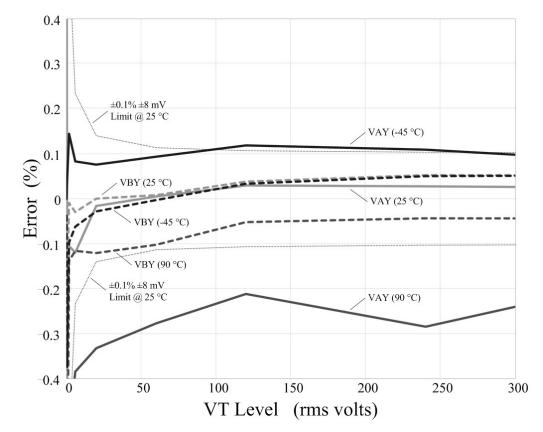

| Figure 7-7:   | VT accuracy. VAY: Isolated Analog Selector VT, VBY: Traditional SEL-421 VT.                                                                                                                                                                      | . 149 |

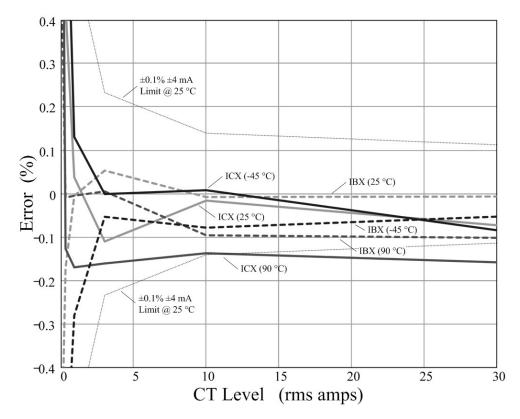

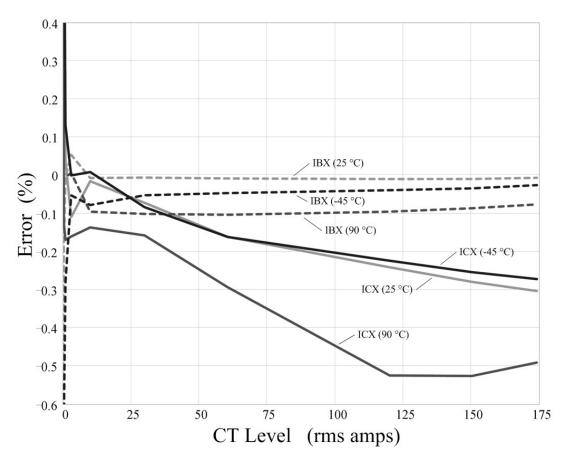

| Figure 7-8:   | CT accuracy. ICX: Isolated Analog Selector CT, IBX: Traditional SEL-421 CT (through 30 A <sub>rms</sub> ).                                                                                                                                       | .150  |

| Figure 7-9:   | CT accuracy. ICX: Isolated Analog Selector CT, IBX: Traditional SEL-421 CT (through 175 A <sub>rms</sub> ).                                                                                                                                      | .152  |

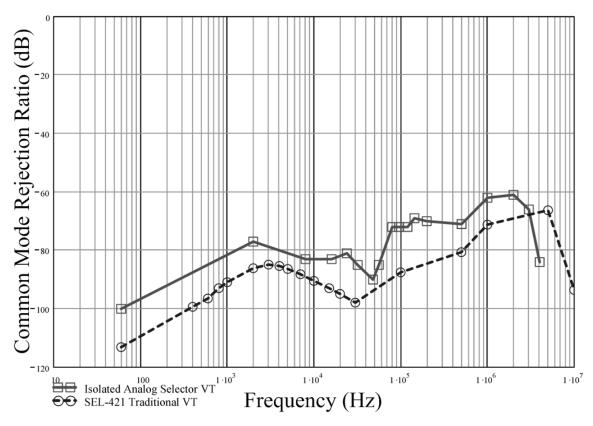

| Figure 7-10:  | Common Mode Rejection Ratio for Isolated Analog Selector and traditional VT.                                                                                                                                                                     | .153  |

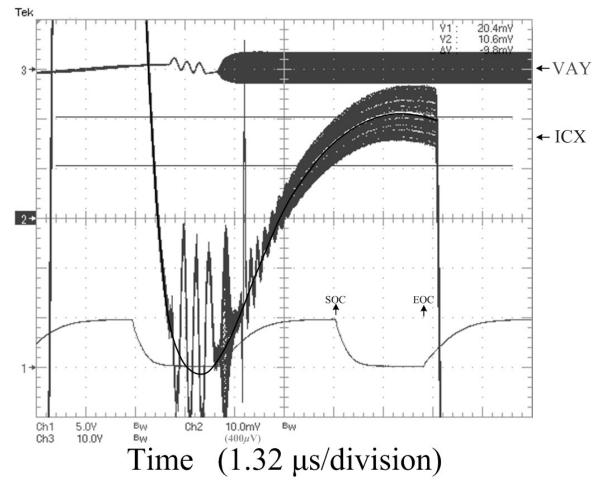

| Figure 7-11: Crosstalk from VAY to ICX. | . 157 |

|-----------------------------------------|-------|

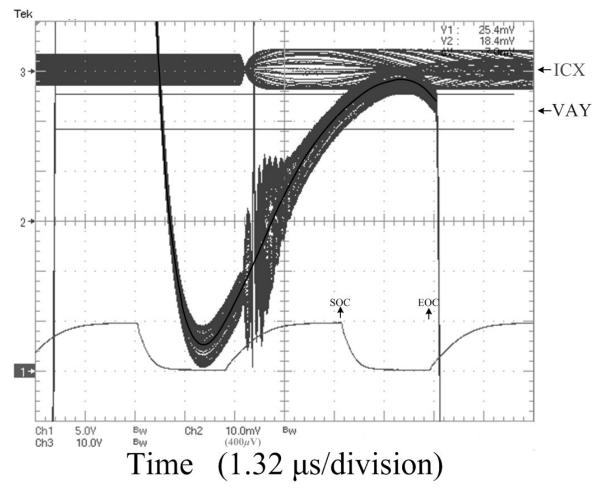

| Figure 7-12: Crosstalk from ICX to VAY. | . 159 |

#### **Chapter 1 Introduction**

Analog acquisition systems are common in digital protective relays (used throughout the power industry), SCADA (Supervisory Control and Data Acquisition) and a vast number of other control and data acquisition systems found in the automotive, industrial and medical fields (to name a few).

A new approach to a transformer isolated analog acquisition system is desirable to reduce the volume and weight of the acquisition components and circuits while maintaining or improving the circuit quality, performance, and cost. The Isolated Analog Selector circuit presented is a significant step towards achieving these goals.

The Isolated Analog Selector circuit greatly reduces the transformer size and weight for a digital protective relay sampling 60 Hz current and voltage signals. The reduction is accomplished by only transforming the analog signal across the isolation barrier for the portion of time needed by the A-D converter for proper conversion to digital sampled data. Instead of requiring an isolation transformer to support the full 60 Hz signal, the isolation transformer only needs to support a limited "snapshot" of the waveform for A-D conversion every sampling interval. High accuracy is achieved even with the reduction in transformer size and weight.

The isolation transformer and other circuitry used in the Isolated Analog Selector are cost effectively implemented and easily assembled using the reliable and high quality printed circuit board processes. Design details and accuracy analysis of the Isolated Analog Selector circuit are presented. Prototype Isolated Analog Selector circuits were built and tested in a digital protective relay. Test results and performance improvements are also presented for prototype implementation.

#### 1.1 Background

Most acquisition systems require some form of isolation between the analog signal to be sampled and the digital control system/computer itself. The isolation is generally needed for safety reasons as well as protection of the digital control system from damage during transients. Digital protective relays, for example, require 2.5 kV of isolation (@ 60 Hz) between the CT (current transformer) and VT (voltage transformer) signals and the digital circuitry of the digital protective relay [1].

Typically, isolation is achieved with an isolation transformer. The transformer consists of a primary winding and a secondary winding that are insulated from each other to meet the isolation requirements. The transformer must be designed to support the current or voltage range of the analog signal as well as the low frequency (50 or 60 Hz) of the analog signal. By design, the transformer secondary analog signal should be a linear representation of the primary analog signal. In other words, the secondary (isolated) analog signal should have the same frequency, a proportional magnitude and a constant phase delay with respect to the primary signal.

Digital protective relays typically use a transformer with an iron-based core (with E-I laminates) to isolate the 60 Hz CT or VT signal. The transformer core is physically big enough to support the largest waveform that is to be measured. The isolation transformer for the CT signal has many known drawbacks. First, for large fault currents (which can have a fully decaying dc offset), the isolation transformer may saturate. Secondly, for

low CT signals, the transformer may become very non-linear. And third, the phase through the isolation transformer is not consistent from part to part or over the entire range of the CT signal.

The construction of iron-based core transformers is a manual labor-intensive process. The Es and Is of the core laminates are manually placed into bobbins (the last few usually being forced). Insulation tape is manually added between primary and secondary magnetic wire layers. The magnetic wires are manually soldered to lead wires or binding post to provide the interface for crimp terminals or wave soldering on a printed circuit board. The transformer is typically impregnated or dipped in varnish to protect the magnetic wires from the environment. These manual steps in the construction of a transformer impact the quality and reliability of the component.

Another issue with iron-based core isolation transformers is the size and weight they add to a device. Digital protective relays, for example, may have twelve isolation transformers that weigh approximately 2/3 pound each for a total of 8 pounds, constituting a significant portion of the relay's size and weight. Each transformer has dimensions of around 1.5" x 1.5" x 2", and cost in the \$5 to \$8 range.

If the analog signal is extremely low frequency (for example various power, frequency, and temperature transducers), conventional isolation transformers cannot be used to isolate the analog signal. Typically, for these types of signals, non-galvanic isolation is achieved with a differential amplifier circuit or galvanic isolation is achieved with an isolation amplifier. Both methods have known drawbacks. The differential amplifier, in addition to not providing galvanic isolation, may have poor common mode

rejection (depending on how closely matched the resistances are). Isolation amplifiers typically are costly and require power supplies on both sides of the isolation module.

Some isolation amplifiers actually convert the analog signal to digital, cross the isolation barrier with the digital data and then convert the digital data back to an analog signal. An acquisition system based on this approach would be more sensibly implemented by leaving the data in digital form and bringing it directly into the digital processor of the control system (i.e. not converting it back to analog first). This would require an A-D converter for each channel located on the input analog signal side of the isolation barrier.

Many acquisition systems require high accuracy for the sampled isolated analog signals. For example, some digital protective relays incorporate a 16 bit A-D converter and need precision of the metered current or voltage to within  $\pm 0.1\%$  of the metered value. For a current or voltage near the lower limit of the specified input range,  $\pm 0.1\%$  may be a few to a small number of counts of the 16 bit A-D converter. It is also important that this accuracy is maintained over operating temperature extremes of the acquisition system circuitry (i.e. -40 to 85 °C).

Conventional differential amplifiers and isolation amplifiers either do not have the necessary precision or are too costly. For a digital protective relay, this type of isolation amplifier may cost many times the conventional iron core CT or VT signal isolation transformer. A key aspect of an analog signal isolation system is high accuracy at a low cost.

Most acquisition systems, for economy of scale purposes, have a single A-D converter that sequentially samples every analog signal (or channel) in the system in a

4

round-robin type fashion. For example, a digital protective relay that has six CT (IAW, IBW, ICW, IAX, IBX, and ICX) and six VT (VAY, VBY, VCY, VAZ, VBZ, and VCZ) input signals, may sequentially sample IAW, IBW, ICW, IAX, IBX, ICX, VAY, VBY, VCY, VAZ, VBZ, and VCZ every 125 µs, or 8 kSPS (kilo samples per second) per channel.

An acquisition system with a single A-D converter requires an analog multiplexer to individually select only one of the channels for conversion by the A-D converter. In addition, as with any sampling acquisition system, a LPF (Low Pass Filter) is required for each channel to prevent aliasing from occurring due to the sampling process.

There are many advantages to reducing the bulkiness of the isolation transformers: reduction in shipping costs (for both the individual transformers as well as the digital protective relay), ease of handling, and reduction in the space requirements for mounting and installation.

The new transformer isolated analog acquisition system significantly reduces the size (1/40 the volume), weight (1/50 the mass), and cost (1/10) of the isolation transformer compared to the traditional digital protective relay CT and VT signal transformers. For a typical digital protective relay, a 2/3 pound isolation transformer can be replaced with a transformer having an E-E ferrite core of around 0.2 ounces, utilizing printed circuit board traces as windings. As discussed in the next section, the reduced transformer size is realized by transformer isolating the CT and VT signal content at a higher switching frequency. The reduction is analogous to switched mode power supply isolation transformers being greatly reduced in size, weight, and cost compared to older style, 50/60 Hz isolation transformers used in linear power supplies.

As with switched mode power supplies, the bulky, single component 50/60 Hz transformer is replaced with a smaller, high frequency, multi-winding transformer plus many additional electronic components for controlling the switching action and providing stability and accuracy to the control circuitry. Although the cost of the transformer is greatly reduced, the additional electronic components have a similar cost compared to the traditional 50/60 Hz transformer. The real advantage is therefore size and weight reduction.

There is a trade off between the isolation transformer size and weight reduction advantages and the greater complexity of the control and support circuitry. The additional electronic components utilize the automated printed circuit board assembly process, which has perceived reliability and quality advantages over the hand assembled, hand soldered traditional CTs and VTs. The greater complexity of the control and support circuitry necessitates a greater attention be given to the design and analysis details of the circuitry as well as the isolation transformer to achieve high accuracy of the sampled data.

#### **1.2 Thesis Scope and Content**

The purpose of this thesis is to 1) introduce the Isolated Analog Selector circuit used in the new transformer isolated analog acquisition system; 2) describe the overall design concept of the Isolated Analog Selector used in the analog acquisition system of a typical digital protective relay; 3) analyze the accuracy of the Isolated Analog Selector circuit and 4) present the test results of a prototype Isolated Analog Selector circuit incorporated into an existing digital protective relay product. An important performance goal of the new transformer isolated analog acquisition system is to achieve a  $\pm 0.1\% \pm 60$  ppm/°C (parts per million per degrees Celsius) accuracy for the VT and CT analog signals being measured. This thesis concentrates on the accuracy analysis of the Isolated Analog Selector, specifically: 1) the stability, settling, and accuracy of the electronic control circuitry used, and 2) the magnetic coupling accuracy of the isolation transformer. The accuracy of the remaining components (signaling resistors, LPF, analog multiplexer, A-D conversion, etc.) are not addressed in this thesis.

Some design details of the new transformer isolated analog acquisition system are not given in this thesis (including input transient protection, signaling resistor requirements, LPF, analog multiplexer, A-D converter). These design details are all aspects of existing digital protective relay products and are not key to the novelty of this new transformer isolated analog acquisition.

There are a few blocks, within the Isolated Analog Selector circuitry itself, where design details are also not provided (including the isolated power supply and triggering or timing circuitry). Although these are important blocks with specific requirements, the design details do not influence the accuracy of the acquired analog data. Therefore, these blocks are only briefly discussed and are assumed to be functioning as required.

The thesis is divided into the following chapters:

Chapter 1: Introduction. The remainder of this chapter provides a concept overview of the control circuitry and multi-winding isolation transformer design (Isolated Analog Selector circuit) for the new transformer isolated data acquisition system.

7

- Chapter 2: Isolated Analog Selector Circuit Design Highlights. Highlights of the Isolated Analog Selector circuit design are provided. An overall block diagram is described and the modes of operation of the new acquisition system are presented.

- Chapter 3: Isolation Transformer Construction Details. Details for the isolation transformer construction used in the Isolated Analog Selector circuit are provided.

- Chapter 4: Isolation Transformer SPICE Modeling. A SPICE (Simulation Program with Integrated Circuit Emphasis) model is developed for the E-E ferrite core, printed circuit board winding transformer used in the Isolated Analog Selector circuit. SPICE models for the part-to-part and temperature extreme variations identify the design constraints of the isolation transformer.

- Chapter 5: Compensation Operational Amplifier Circuit Performance. SPICE models of the electronic control circuitry used in the Isolated Analog Selector help identify, measure, and improve the stability and accuracy of the design.

- Chapter 6: Isolation Transformer Magnetic Coupling Accuracy. An FEA (Finite Element Analysis) tool is used to determine the accuracy of the isolation transformer of the Isolated Analog Selector. The FEA tool assists in improving the isolation transformer's coupling accuracy by identifying the optimum placement of traces for the printed circuit board windings.

Chapter 7: Prototype Testing and Results. The test results of a prototype Isolated Analog Selector circuit incorporated into an existing digital protective relay product are presented.

Chapter 8: Conclusions

#### **1.3 Isolated Analog Selector Circuit Overview**

The new transformer isolated data acquisition system employs an Isolated Analog Selector circuit for each analog input channel. The purpose of the Isolated Analog Selector circuit is to produce a high accuracy voltage output signal for the corresponding analog input channel, through an isolation transformer, for the portion of time needed for proper A-D conversion.

#### **1.3.1** Concept

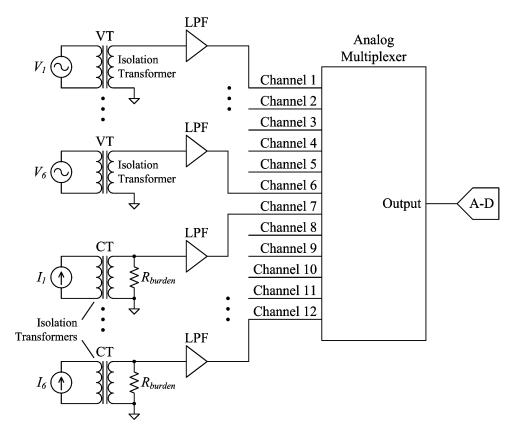

A traditional digital protective relay may have six VT (voltage transformer) and six CT (current transformer) analog input channels that are sampled at 8000 samples/second using a single A-D converter [2]. A block diagram of the acquisition system for this digital protective relay is shown in Figure 1-1.

Figure 1-1: Block diagram of a traditional acquisition system for a digital protective relay with six VT and six CT channels.

The VTs of Figure 1-1, in addition to providing 2.5 kV isolation, also step down the voltage to a level that is within the range of the A-D converter. The magnetic flux density, B, of the VT core is related to the integral of the voltage waveform, V(t), applied to the VT [3]:

$$B(t) = \frac{1}{NA_e} \int V(t)dt, \qquad (1-1)$$

where N is the number of turns and  $A_e$  is the effective cross sectional area of the core.

To avoid transformer core saturation (i.e. extreme non-linear behavior), the magnetic flux density must stay below the magnetic flux density saturation level,  $B_{sat}$ . From (1-1), transformer core saturation occurs, for a positive voltage waveform, when the volt-time product (i.e. integration of the voltage waveform) reaches  $B_{sat}NA_e$ . Therefore the

transformer must be designed (i.e. have a magnetic flux density saturation,  $B_{sat}$ , effective cross sectional core area,  $A_e$ , and number of turns, N) to support the applied volt-time product. For example, if the range of the A-D converter is  $\pm 3$  Vdc, then a symmetrical, full scale, 50 Hz voltage signal requires the transformer to support approximately  $\pm 9$ V·ms (integration of the 3 V<sub>p</sub> waveform).

The CTs of Figure 1-1, in addition to providing 2.5 kV isolation, step down the current to a level such that the voltage across the burden resistor,  $R_{burden}$ , (due to the output current of the CT) is within the range of the A-D converter.

Since the A-D converter is sampling at 8000 samples/second, the acquisition system is capable of measuring harmonics of the 50 or 60 Hz signals up to the 16<sup>th</sup> harmonic. The lower harmonics are important for some digital protective relay algorithms and harmonics up to the 16<sup>th</sup> can be used to infer power quality of the VT and CT signals.

The anti-aliasing LPFs (Low Pass Filters) are necessary to remove high frequency components and prevent them from aliasing to the low-pass band [4]. For the sampling rate of 8 kHz, the low-pass band should be less than the folding frequency of 4 kHz (1/2 the sampling frequency). A 2<sup>nd</sup> order LPF with a corner frequency around 2 kHz does a good job of passing the 16<sup>th</sup> harmonic while attenuating any frequency above 4 kHz that may fold back by at least 20 dB.

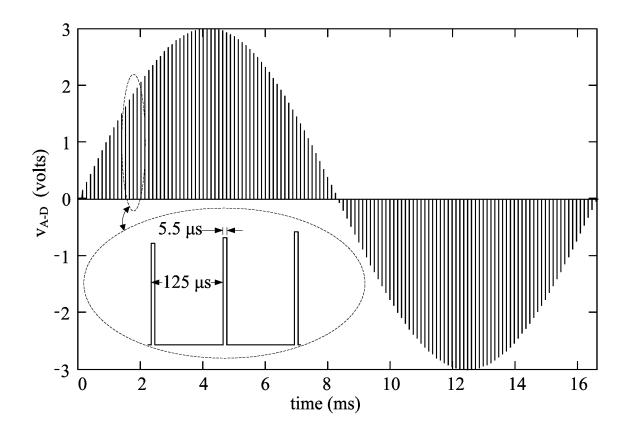

The A-D converter, completing a conversion approximately every 5.5  $\mu$ s, sequentially samples the 12 channels at a sampling rate of 8 kHz (i.e. each channel is sampled every 125  $\mu$ s). The A-D converter only has 'access to' any given channel's analog signal for 5.5  $\mu$ s every 125  $\mu$ s.

As an illustrative example, a full scale 60 Hz ac voltage signal is applied to  $V_1$ . If the signals from the other channels are ignored, or blanked out, the voltage signal at the output of the analog multiplexer (connected to the A-D converter) is portrayed in Figure 1-2. During the remainder of the 125 µs interval (depicted in the expanded oval of Figure 1-2), the A-D converter is sampling Channel 2 through Channel 12, monitoring other analog quantities, and idle for the remainder of time.

Figure 1-2: Voltage signal at the A-D converter, with a 60 Hz ac voltage signal on Channel 1 and the signals from the other channels blanked out.

Since the A-D converter only utilizes Channel 1's signal for 5.5  $\mu$ s every 125  $\mu$ s, there is no system requirement to bring the entire 60 Hz signal across the isolation barrier. It is this reduced requirement that drives the design of the new transformer isolated analog acquisition system.

If the isolated voltage signal is applied only for the portion of time needed for proper A-D conversion, then the volt-time requirement of the isolation transformer can be greatly reduced. For example, if the A-D converter (with the  $\pm$  3 Vdc range mentioned earlier) has a conversion time of around 2.5 µs (plus another 8 µs for the signal to settle before A-D conversion begins), then the volt-time requirement of the isolation transformer can be reduced to around 31 V·µs (i.e. nearly 1/300 of the volt-time is needed).

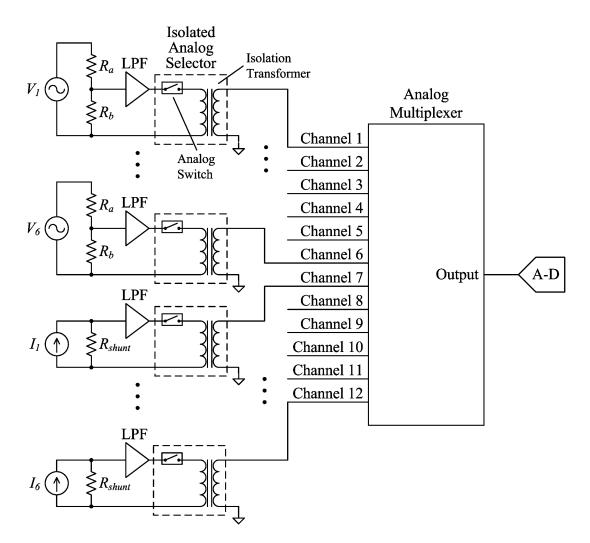

Conceptually, the anti-aliasing LPF is moved to the other side of the isolation barrier and the isolation transformer is only driven at the appropriate time for proper A-D conversion of the channel. A concept block diagram of this new transformer isolated data acquisition system is shown in Figure 1-3. Two basic building blocks of the 'Isolated Analog Selector' circuit are the analog switch and isolation transformer as shown in Figure 1-3.

Figure 1-3: Concept block diagram of a new transformer isolated data acquisition system.

A resistor divider,  $R_a$  and  $R_b$ , divides down the voltage to a level within the range of the A-D converter for the voltage channel inputs shown in Figure 1-3. A shunt resistor,  $R_{shunt}$ , converts the input current to a voltage level also within the range of the A-D converter for the current channel inputs shown in Figure 1-3.

The analog switch, in a given Isolated Analog Selector, closes approximately 5  $\mu$ s prior to the corresponding channel being selected by the analog multiplexer, allowing the switching transients to settle before the signal is multiplexed to the A-D converter. Once the A-D conversion is complete, the analog switch then opens. The result is that the

channel analog signal presented to the A-D converter (depicted in Figure 1-2 for Channel 1) are essentially the same for this new transformer isolated data acquisition system (shown in Figure 1-3) compared to a traditional acquisition system (shown in Figure 1-1).

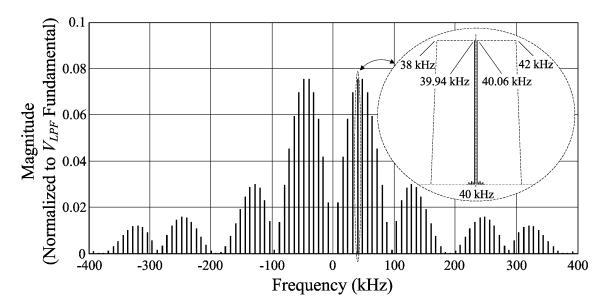

The opportunity to reduce the isolation transformer's core size is also recognized in the frequency domain. The turning on and off of the analog switch, in the Isolated Analog Selector of Figure 1-3, in effect multiplies the LPF output voltage signal by a unity amplitude square wave pulse train (pulse width,  $\tau = 10.5 \ \mu$ s) with a period of T = 125  $\mu$ s. The spectral content of this pulse train is the well known  $\sin(\pi f \tau)/\pi f \tau$  envelope, with zero crossings at multiples of  $1/\tau$ , and discrete spectral content at multiples of  $1/T = 8 \ \text{kHz}$  [5]. Due to the on and off action of the analog switch, the spectral content of the LPF output signal is convolved with the spectral content of the on/off analog switch action [6].

The actual spectral content that the isolation transformer is subjected to must also include the voltage signal that occurs after the analog switch is opened. Any energy in the core causes the transformer winding voltage to reverse polarity (i.e. flyback) when the analog switch opens. The flyback voltage is clamped to a supply rail until the core energy is depleted (i.e. the core is reset). Further details of the core reset are provided later in Chapter 2. Therefore, the on/off action that the transformer is subjected to can be approximated by the unity amplitude square wave pulse (mentioned above) followed by a negative unity amplitude pulse of the same width.

The approximated spectral content of the transformer on/off switching action (positive pulse followed by a negative pulse) convolved with the spectral content of a typical LPF output voltage signal,  $V_{LPF}$  (60 Hz system), is shown in Figure 1-4 (normalized to the rms fundamental of  $V_{LPF}$ ).

Figure 1-4: Approximated spectral content of the transformer on/off switching action convolved with the spectral content of a typical LPF output voltage signal,  $V_{LPF}$  (normalized to the rms fundamental of  $V_{LPF}$ ).

Due to convolution in the frequency domain, the spectral content of the typical LPF output voltage signal is present at each multiple of 8 kHz as depicted in the expanded oval of Figure 1-4. The dashed trapezoid in the expanded oval shows the pass band characteristic of the LPF with corner frequency around 2 kHz (roll off purposely exaggerated).

As shown in Figure 1-4, there is no dc content to the isolation transformer's voltage spectrum. The lowest frequency content is at 6 kHz. The on/off action of the analog switch converts the voltage spectrum that was at 50 or 60 Hz (plus any harmonics present through the 16<sup>th</sup> harmonic) to a voltage spectrum that is spread out above 6 kHz. Similar to switched mode power supplies, the isolation transformer only needs to support the higher frequencies and therefore can be reduced in size.

The new transformer isolated acquisition system significantly reduces the volt-time requirement of the isolation transformer (from 9 V·ms to 31 V·µs for the voltage channel

input). The reduced volt-time product can easily be supported with a small E-E ferrite core. This has the advantage of significantly shrinking the size and weight of a digital protective relay that has 12 transformers. However, with the reduced core size comes a similar reduction in the magnetizing inductance. The challenges of the diminished magnetizing inductance are addressed next.

#### **1.3.2** Design Challenges and Design Progression

As with any transformer design, the effect of the magnetizing inductance,  $L_m$ , introduces an error in the transformed voltage signal (i.e. the secondary voltage does not exactly match the expected ratio of the primary voltage). This error is predominantly a result of the magnetizing current flowing through the primary winding resistance and primary leakage inductance [7].

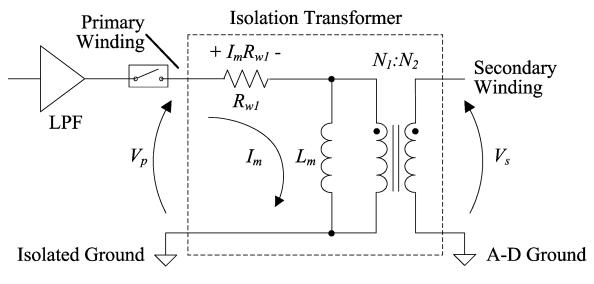

A first approximation circuit model for the isolation transformer of Figure 1-3 is shown in Figure 1-5 (ignoring the primary leakage inductance).

Figure 1-5: First approximation circuit model for the isolation transformer.

If at time, t = 0, the analog switch closes and a dc voltage,  $V_p$ , is applied to the primary winding of the isolation transformer, the magnetizing current,  $I_m$  (initially 0 A), rises and settles in an exponential fashion to a final value of  $V_p/R_{wI}$ :

$$I_m(t) = \frac{V_p}{R_{wI}} \Big( 1 - e^{-tR_{wI}/L_m} \Big).$$

(1-2)

When the analog switch first closes, the current can be linearly approximated with a ramp (as long as the input voltage,  $V_p$ , remains constant):

$$I_m(t) \cong \frac{V_p t}{L_m} \quad (t \ll L_m/R_{wI}).$$

(1-3)

From (1-3), smaller cores (i.e. smaller magnetizing inductance,  $L_m$ ), result in the magnetizing current,  $I_m$ , ramping up quicker when a dc primary voltage is first applied. This ramping magnetizing current will produce a ramping voltage drop across the winding resistance,  $R_{w1}$  (as shown in Figure 1-5), and causes the secondary voltage to droop (in error):

$$V_{s}(t) = \left(V_{p} - I_{m}(t)R_{wI}\right)\frac{N_{2}}{N_{I}}.$$

(1-4)

The error of (1-4) increases as time progresses. For the reduced size, E-E ferrite core (used in the isolation transformer of the Isolated Analog Selector) the typical magnetizing inductance,  $L_m$ , is around 250 µH and the resistance of the printed circuit board trace primary winding is around 1.3  $\Omega$ . After 10 µs, this gives an error in the secondary voltage of nearly 5 %. This is too much error since the overall required accuracy of the analog

acquisition system is  $\pm 0.1$  %. Since the inductance of the E-E ferrite core is non-linear, a simple gain adjustment/calibration is ineffective.

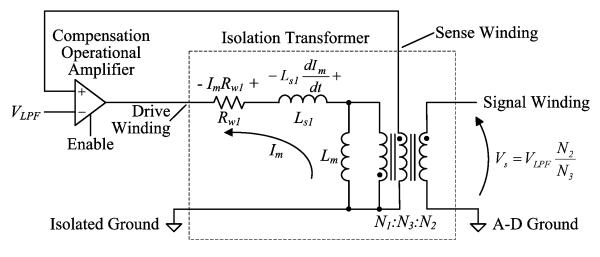

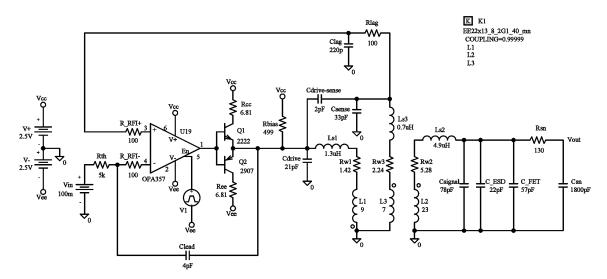

Orders of magnitude reduction in the error due to the magnetizing current is achieved by adding a compensating operational amplifier circuit. A third, sense winding is also added to the transformer to provide feedback to the compensation operational amplifier as shown in the Isolated Analog Selector circuit concept block diagram of Figure 1-6.

Figure 1-6: Isolated Analog Selector circuit concept block diagram.

The compensation operational amplifier has an output enable feature (similar role as the analog switch of Figure 1-5). When the compensation operational amplifier is enabled, the output drives the drive winding. The sense winding provides feedback to the compensation operational amplifier. Even though the sense winding is connected to the positive input terminal of the compensation operational amplifier, it is negative feedback since the drive winding has an opposite polarity with respect to the sense winding.

With this compensation operational amplifier circuit, the voltage drops of the primary winding resistance,  $R_{wI}$ , and leakage inductance,  $L_{sI}$ , do not result in an error at the secondary voltage,  $V_s$ . If a positive dc voltage is at  $V_{LPF}$  when the compensation

operational amplifier is enabled, the output of the compensation operational amplifier will adjust negative and continue to ramp down in order to maintain the sense winding voltage (at the positive terminal of the operational amplifier) at a nearly equivalent level to  $V_{LPF}$  (at the negative terminal of the operational amplifier).

To a first approximation, the output voltage on the signal winding,  $V_s$ , is equal to the LPF voltage,  $V_{LPF}$ , adjusted by the turns ratio  $N_3:N_2$ . This, of course, assumes that there is no load on the secondary of the isolation transformer and that the operational amplifier is ideal. In reality there is some secondary output loading and the operational amplifier has some finite gain and some input impedance and other non-ideal characteristics.

The compensation operational amplifier is a key component to the Isolated Analog Selector control system, shown in the block diagram of Figure 1-6. The control system circuitry must be designed with adequate stability, loop gain, and settling characteristics in order to achieve high accuracy.

Additionally, the LPF, compensation operational amplifier, and other active circuitry on the primary side of the Isolated Analog Selector (i.e. left side of the isolation transformer of Figure 1-6) need power supply rails. These power supply rails must be isolated from the secondary side (i.e. isolated from the right side or signal winding of the isolation transformer of Figure 1-6). Therefore, the Isolated Analog Selector circuit must also contain an isolated power supply.

Finally, the compensation operation amplifier must be enabled for an adequate amount of time (for signal settling and proper A-D conversion) at the right time (just prior to the A-D conversion of the corresponding channel). The controlling of the enable for the compensation operational amplifier must originate from the signal winding side, and therefore must cross the isolation barrier (2.5 kV isolation required between isolated ground and A-D ground of Figure 1-6).

The details of the compensation operational amplifier circuit (stability, settling and accuracy) are given in Chapter 5. The next chapter gives some highlights of the Isolated Analog Selector circuit design.

#### **Chapter 2 Isolated Analog Selector Circuit Design Highlights**

Other circuit components (not shown in Figure 1-6) are required around the compensation operational amplifier for stability and improved accuracy. When the Isolated Analog Selector circuit is not driving the voltage signal across the isolation barrier (i.e. the compensation operational amplifier of Figure 1-6 is not enabled), the isolation transformer is further utilized for:

- 1. A forward converter switched mode power supply to generate isolated power rails for the LPF and compensation operational amplifier circuitry. The forward converter is driven by FETs connected to the signal winding.

- Transferring a trigger signal across the isolation barrier that enables the compensation operational amplifier of Figure 1-6 at the appropriate time for proper A-D conversion. The trigger signal is generated by the same FETs used for the forward converter switched mode power supply.

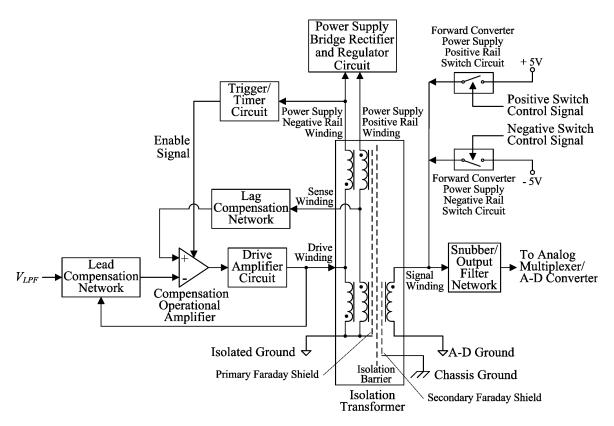

A block diagram for the Isolated Analog Selector circuit is shown in Figure 2-1. The output of the LPF,  $V_{LPF}$ , is the input to the Isolated Analog Selector (left/primary side of Figure 2-1) and is referenced to isolated ground. The output of the Isolated Analog Selector (right/secondary side of Figure 2-1) connects to the analog multiplexer and is referenced to A-D ground. The circuit block diagram of Figure 2-1 shows the details of the Isolated Analog Selector blocks of Figure 1-3.

Figure 2-1: Isolated Analog Selector circuit block diagram.

The lead compensation network, lag compensation network, drive amplifier circuit, and snubber/output filter network blocks of Figure 2-1 are all necessary for the stability and accuracy of driving the signal across the isolation barrier when the compensation operational amplifier is enabled. The details of these blocks are given in Chapter 5.

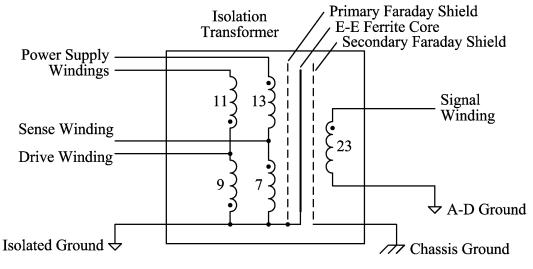

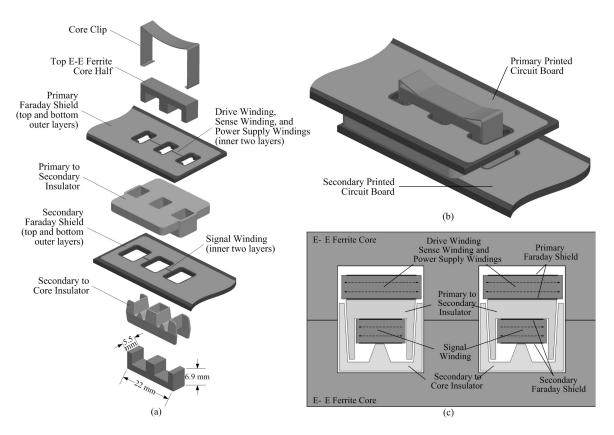

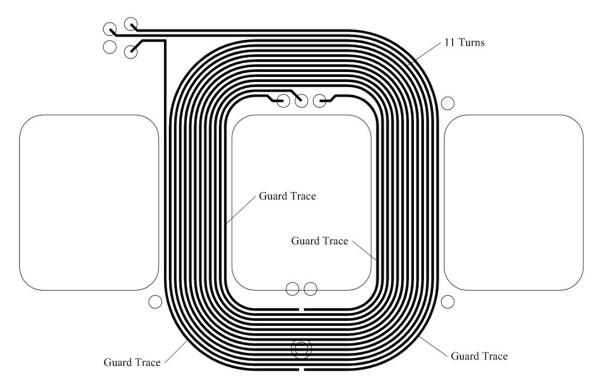

The isolation transformer consists of an E-E ferrite core with printed circuit board traces for the drive, sense, signal, and power supply windings. The primary and secondary Faraday shields along with the construction details of the isolated transformer are given in Chapter 3.

The forward converter power supply positive rail and negative rail switch circuits in the upper right of Figure 2-1 contain FETs that are used for a forward converter/push-pull switched mode power supply. When the compensation operational amplifier is disabled, the FETs alternately drive the signal winding (between + 5 Vdc and – 5 Vdc) producing alternating feed forward voltages across the isolation barrier on the power supply positive and negative rail windings. These power supply windings provide energy to the power supply bridge rectifier and regulator circuit block of Figure 2-1 which produces the isolated power supply rails for the LPF, compensation operational amplifier, drive amplifier circuit, and trigger/timer circuit.

The FETs in the forward converter power supply positive rail and negative rail switch circuits are also used to send a trigger signal across the isolation barrier to the trigger/timer circuit block of Figure 2-1. When the trigger/timer circuit block detects the trigger signal, it pulses the enable signal for approximately 12  $\mu$ s. This gives ample time to allow the compensation operational amplifier and drive amplifier circuit to drive the drive winding and have the signal winding settle before and during A-D conversion.

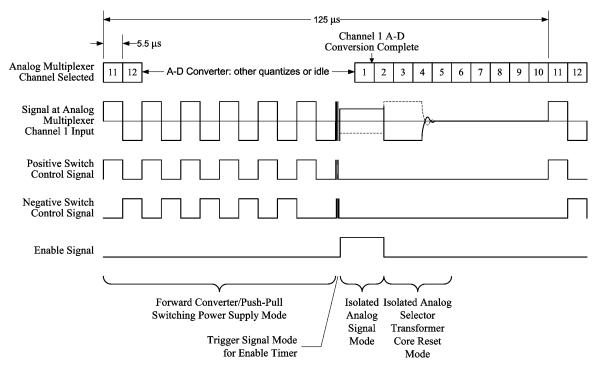

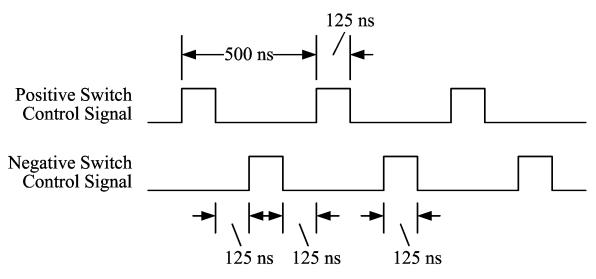

A timing diagram of the four modes of the Isolated Analog Selector circuit (for Channel 1) is given in Figure 2-2. The positive and negative switch control signals are used to control these four modes and originate from the digital controller/processor controlling the analog acquisition system.

Figure 2-2: Isolated Analog Selector Channel 1 Timing Diagram.

The first operation mode shown in Figure 2-2 is the forward converter/push-pull switching power supply mode. During this mode (for Channel 1), the A-D converter happens to be sampling Channels 11 and 12 as well as other analog quantities and then remains idle. In this operation mode, the positive and negative FETs (switches in the upper right of Figure 2-1) are alternately switched back and forth to drive the push/pull forward converter switched mode power supply. During the first mode of operation, energy is fed into the power supply bridge rectifier and regulator circuit block of Figure 2-1. This energy is used to provide the isolated power supply rails for the LPF, compensation operational amplifier, drive amplifier circuit, and trigger/timer circuit of Figure 2-1.

When the positive switch control signal (of Figure 2-2) is high (for around 5.5  $\mu$ s), the forward converter power supply positive rail switch (of Figure 2-1) turns on and +5

Vdc is applied to the signal winding, producing a positive voltage on the power supply positive rail winding and a negative voltage on the power supply negative rail winding of Figure 2-1. Likewise, when the negative switch control signal is high (for around 5.5  $\mu$ s), the forward converter power supply negative rail switch turns on and -5 Vdc is applied to the signal winding, producing a negative voltage on the power supply positive rail winding of Figure 2-1.

Storage capacitors in the power supply bridge rectifier and regulator circuit block (of Figure 2-1) maintain the isolated power supply rails during the remaining modes of operation.